Hi Experts,

Our customer found there is click noise and is guessing a cause is from clock synchronization. The noise is sometimes periodically but sometimes not heard.

the datasheet describes as below in 9.3.2.1

If the relationship between LRCK and system clock changes more than ±5 SCK, internal operation (using an onchip oscillator) is initialized within one sample period and analog outputs are forced to the bipolar zero level until resynchronization between LRCK and system clock is completed.

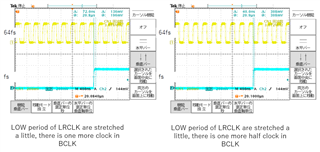

Customer's clocks is that LRCK and BCK is synchronized, but LRCK and SCK is not.

I want to check if my understanding is correct or not that "more than +/-5 SCK change" means the rising edge of LRCK differs from SCK more than +/-5 SCK?

Can you please explain in more detail? Also do you think clock synchronization leads click noise?

Best regards,

Hideki