Hello, expert,

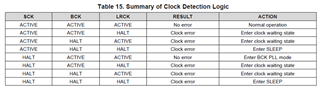

I received question about Clock Halt and Error Detect for PCM1862.

When CLK was changed without CLK halt as follows, from 44.1kHz x to 48kHz, will it be regarded as CLK error?

SCLK 22.579MHz ⇒24.576MHz

BCLK 2.822MHz ⇒3.072MHz

LRCK 44.1KHz ⇒ 48 kHz

If so, should PCM1862 will automatically re-operate after CLK error detected as follows sequence, which is written in 9.3.9.7 Clock Halt and Error Detect?

1. Mute audio output immediately (without volume ramp down)

2. Wait until proper clock is supplied (known as Clock Waiting State)

3. Restart clock detection. The PLL and all clock dividers are reconfigured with the result of the detection.

4. Start fade-in

Best regards,

Koki Tsushima