Hello,

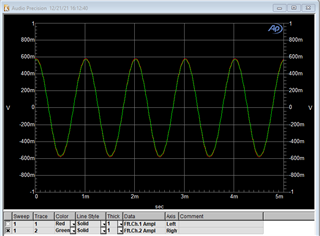

I’m doing TLV320AIC3101 codec chip performance verification and then will use AIC3101 chip for audio system design. According to TLV320AIC3101’s datasheet, there exist a passive analog bypass mode, in which MIC1LP/LINE1LP input signal or MIC2LP/LINE2LP input signal to the LEFT_LOP and MIC1RP/LINE1RP input signal or MIC2RP/LINE2RP to the RIGHT_LOP can be connected by closing switches SW-L1, SW-L2, SW-R1, SW-R2( Meanwhile, need to open switches SW-L0, SW-L3, SW_R0, SW-R3). The one needs to write register page 0, register 108 bit 0/1/2/4/5/6, in order to do this. When I checked these passive bypass mode paths, I found MIC1LP/LINE1LP, MIC1RP to the LEFT_LOP and RIGHT_LOP were functionally correct. However, the connections from MIC2L/LINE2L to the LEFT_LOP and MIC2R/LINE2R to the RIGHT_LOP were no function. That means the switches of SW-L2 and SW-R2 are not controlled by the page 0, register 108 bit 6 and bit 2. How could I confirm the switches of SW-L2 and SW-R2 not worked? Firstly I set the page 0, register 108 bit 6 and bit 2 setting to 1, and then used the multimeter to measure the resistances between the pin MIC2L/LINE2L and the pin LEFT_LOP, the pin MIC2R/LINE2R and RIGHT_LOP. The results were infinite. As the contrast, when I set page 0, register 108 both bit 4 and bit 0 to 1, I could get resistances for MIC1LP to LEFT_LOP, MIC1RP to RIGHT_LOP in about 310ohms ~ 330ohms. This illustrated the switches of SW_L1 and SW-R1 successfully closed. In the meantime, I used signal gen to send sine wave to MIC1LP and MIC1RP and observed the sine wave outputs at LEFT_LOP and RIGHT_LOP. But when I selected switches of SW-L2 and SW-R2, I could not observed the sine wave at the output pins of LEFT_LOP and RIGHT_LOP. I checked the TLV320AIC3101 datasheet related description many times and confirmed what I did was correct. But the switches of SW-L2 and SW-R2 not workable. As a primary result, I doubt TLV320AIC3101 datasheet exist description error? So would you mind confirming the description for the switches of SW-L2/SW-R2 and page 0, register 108 no problem inside TI?