PM4201

- What's the difference between master mode and slave mode of PCM4201; what applications are they used for, in my case, I want to realize sound source localization via microphone arrays, and I will use FPGA as controller.(By the way, is it possible to interface this ADC with FPGA?)

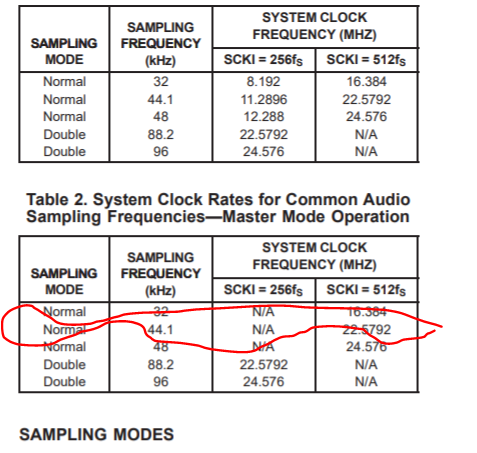

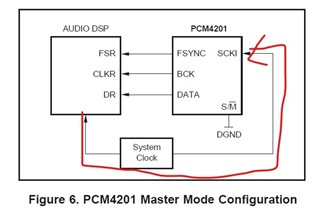

- The system clock is used to provide sampling frequency reference and it goes to audio DSP and ADC. But in master mode, the PCM4201 generates the FSYNC and BCK clocks to communication, then I would liek to ask what's the usage of this system clock for audio DSP?