Other Parts Discussed in Thread: TAS2552

Hi Team,

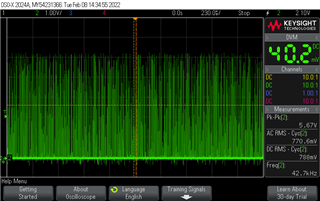

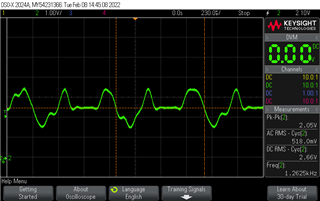

Recently we have replaced our old audio chip with TAS2553. But I couldn't get the desired audio output in the speaker as an earlier chip. I am getting very very low audio in the speaker out.

I have read and verified all the configuration registers.

1 ) I2S digital Input,

2) I2S WCLK configured as 22.05 khz

3) I have measured the frequency as BCLK -> 705 khz I2S_MCLK -> 5.6 MHZ

4) I am trying to play a 22ksps/48K sps audio file. I have switched the I2S frequency to 48K when playing the 48Ksps file.

I have configured as below,

uint8_t Device_config1_Array[2] ={TAS2553_CFR1,(CFR0_SWS_SHUTDOWN)};

uint8_t Device_config2_Array[2] ={TAS2553_CFR2,(CFR2_CLASSD_EN|CFR2_BOOST_EN|CFR2_IVSENSE_EN|CFR2_RESERVED_CFG)};//Reserved. MUST BE WRITTEN TO ZERO DURING

uint8_t Device_config3_Array[2] ={TAS2553_CFR3, (CFR3_PDM_IN_SEL|CFR3_DIN_SOURCE_AVG|CFR3_I2S_OUT_SEL|CFR3_WCLK_22KHZ)};

uint8_t Serial_Interface_CTRL_Array[2] ={TAS2553_SERIAL, (SERIAL_WORD_16 | SERIAL_DATA_I2S|SERIAL_CLKPERFRAME_32)};

uint8_t Level_ctrlreg_Array[2] ={TAS2553_LEVEL_CTRL, 0xA9};//Write to 0xA9 during initialization. See Initialization.

uint8_t PGA_Gain_Array[2] ={TAS2553_PGA_GAIN, PGA_GAIN_24db };//PGA_GAIN_0db

uint8_t Edge_Rate_CTRL_Array[2] ={TAS2553_CLASSD_RATE,(CLASSD_EDGE_CTRL_14ns)};

uint8_t Boost_Autopass_CTRL_Array[2] ={TAS2553_BOOST_AUTOPASS,(CLASSD_EDGE_CTRL_50ns)};

uint8_t Hystime_Lmtrate_Array[2] ={TAS2553_HYST_LIMIT,0x20};

uint8_t PLL_CtrlReg1_Array[2] ={TAS2553_PLL_REG1,(0x08 &TAS2553_PLL_J_MASK )}; //J = 8;

uint8_t PLL_CtrlReg2_Array[2] ={TAS2553_PLL_REG2,TAS2553_PLL_D_UPPER(0x1e)} ; // PLL set, uppder D =0

uint8_t PLL_CtrlReg3_Array[2] ={TAS2553_PLL_REG3,TAS2553_PLL_D_LOWER(0x5b)} ; // PLL set, Lower D =1

Kindly help me to fix the audio.