Hi team,

0, 00 1, 00 2, aa 3, 91 4, c0 5, 00 6, 00 7, 1e 8, 00 9, 07 10, 00 11, 01 12, 5f 13, 00 14, 00 15, 50 16, 50 17, ff 18, ff 19, 00 20, 78 21, 00 22, 00 23, 78 24, 00 25, 80 26, 00 27, fe 28, 00 29, 00 30, fe 31, 00 32, 6c 33, 1e 34, 00 35, 00 36, cc 37, 00 38, 00 39, 00 40, 80 41, 01 42, 00 43, 00 44, 00 45, 00 46, 00 47, 80 48, 00 49, 00 50, 00 51, 0e 52, 00 53, 00 54, 00 55, 00 56, 00 57, 00 58, 06 59, 00 60, 00 61, 00 62, 00 63, 00 64, 80 65, 0e 66, 00 67, 00 68, 00 69, 00 70, 00 71, 00 72, 06 73, 00 74, 00 75, 00 76, 00 77, 00 78, 00 79, 00 80, 00 81, 00 82, 80 83, 00 84, 00 85, 00 86, 98 87, 00 88, 00 89, 00 90, 00 91, 00 92, 80 93, 08 94, ce 95, 00 96, 00 97, 00 98, 00 99, 00 root@udx710-module:/sys/bus/i2c/devices/3-0018#

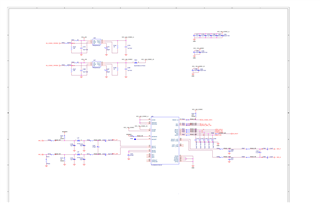

We are a 26MHz MCLK with a sampling rate of 8K and 16 bits. BCLK is output. But our sound card has no sound. We suspect a register configuration problem.

Please give us some suggestions, if it is convenient.

If we don't have a clear description, please reply to us.

Best Regards,

Jiahui