I am developing with the PCM4104 on a custom board, but I am not getting any output. I am expecting a 1 kHz sine wave.

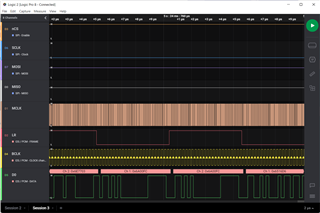

Here is my SPI configuration (after software reset):

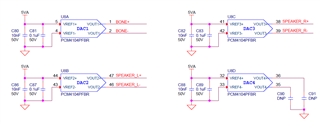

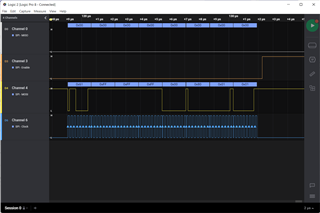

I am sending 24-bit I2S audio data (full scale 24-bit sinusoid):

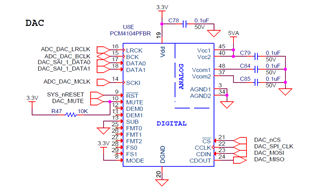

This is the schematic of the part:

Voltage references are +5 / GND.

Any help at all would be greatly appreciated.

Bill