Previously I reported on problems I was having with the DIR on the SRC4392.

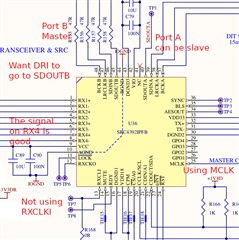

Since then we have put the SRC4392 onto our PCB and while most feature seem to be working I am still having trouble with the DIR. Here is my situation :

I am outputting audio over the DIT and then the DIT is connected to the DIR on input 4. The port B I2S bus is configured to input the signal from the DIR output. The single board computer (SBC) is used to generate and capture audio like this :

SBC -> port B -> DIT -> DIR -> port B -> SBC

Unfortunately the DIR doesn't seem to be working. The clocks aren't being locked and there is no audio coming out of the DIR.

I have absolutely no idea what is wrong with this setup. It is the same problem I was having which I reported in the other question to the forum - which also had no solution. I am a little concerned that this chip is on our PCB and we can't get it to work as a DIR.

Here are the current register settings :

01: 3f

02: 00

03: 09

04: 00

05: 29

06: 03

07: 68

08: 00

09: 00

0a: 00

0b: 00

0c: 00

0d: 1b

0e: 17

0f: 22

10: 00

11: 00

12: 00

13: 00

14: 00

15: 00

16: 00

17: 00

18: 00

19: 00

1a: 00

1b: 00

1c: 00

1d: 00

1e: 00

1f: 00

20: 00

21: 00

22: 00

23: 00

24: 00

25: 00

26: 00

27: 00

28: 00

29: 00

2a: 00

2b: 00

2c: 00

2d: 00

2e: 00

2f: 00

30: 00

31: 00

32: 00

33: 00

status regs below

12: 00

13: 00

14: 00

15: 00

16: 00

17: 00

18: 00

19: 00

1a: 00