Hi,

I am updating queries with respect to below thread

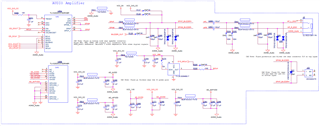

I have tested speaker , but it is giving noise while playing audio. Any suggestion how I can ressolve this issue. I had tried to tune the gain value but still there is noise whether need to configure any register ?

Regards,

Deeksha