Other Parts Discussed in Thread: ADC5140EVM-PDK

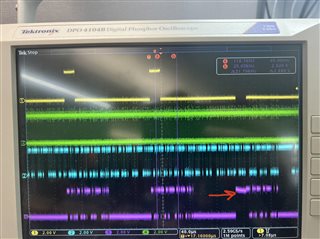

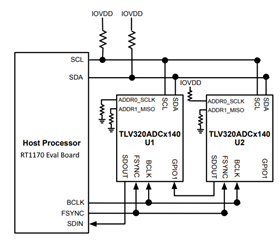

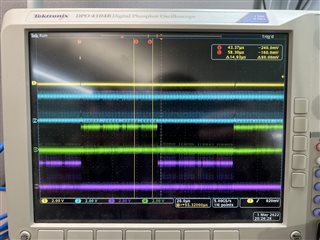

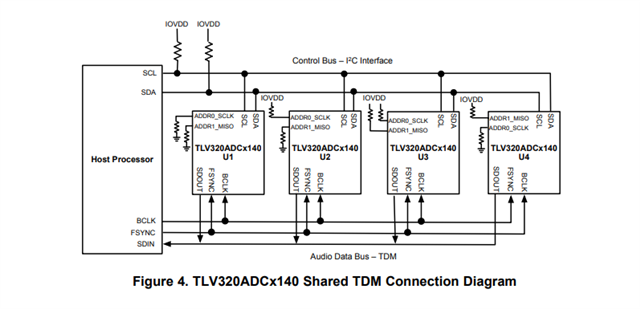

Hello! I need some help on an issue where I have two ADC5140 ADCs configured in daisy chain mode (as per figure 9 in the app note : Multiple TLV320ADCx140 Devices With Shared TDM and I 2C Bus). I am using TDM mode, 24 bits, 8 channels (4 from the first ADC, 4 from the second). It is working for the most part, but randomly I am getting all 0's or all 1's from the first channel of the last ADC on the chain. I have attached a scope shot that illustrates the issue. My initialization code is as follows:

// Pull HW reset low, wait 10ms, then release

CLR_ADCMASTER_RESET;

SysTick_Delay_ms(10);

SET_ADCMASTER_RESET;

SysTick_Delay_ms(10);

// ADC 1 /////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

LPI2C1_Write(I2C_ADDR_ADC1, ADCX140_PAGE_SELECT, 0x00); // Set page to zero

LPI2C1_Write(I2C_ADDR_ADC1, ADCX140_SLEEP_CFG, 0x81); // Wake up and enable AREG

SysTick_Delay_ms(10);

LPI2C1_Write(I2C_ADDR_ADC1, ADCX140_ASI_CFG0, 0x20); // 24 bit words

LPI2C1_Write(I2C_ADDR_ADC1, ADCX140_ASI_CFG1, 0x00);

LPI2C1_Write(I2C_ADDR_ADC1, ADCX140_ASI_CH1, 0x00); // Mapped to default slots

LPI2C1_Write(I2C_ADDR_ADC1, ADCX140_ASI_CH2, 0x01);

LPI2C1_Write(I2C_ADDR_ADC1, ADCX140_ASI_CH3, 0x02);

LPI2C1_Write(I2C_ADDR_ADC1, ADCX140_ASI_CH4, 0x03);

LPI2C1_Write(I2C_ADDR_ADC1, ADCX140_BIAS_CFG, 0x60);

LPI2C1_Write(I2C_ADDR_ADC1, ADCX140_CH1_CFG0, 0x80); // Line input, differential, AC Coupled

LPI2C1_Write(I2C_ADDR_ADC1, ADCX140_CH2_CFG0, 0x80); //

LPI2C1_Write(I2C_ADDR_ADC1, ADCX140_CH3_CFG0, 0x80); //

LPI2C1_Write(I2C_ADDR_ADC1, ADCX140_CH4_CFG0, 0x80); //

LPI2C1_Write(I2C_ADDR_ADC1, ADCX140_DSP_CFG0, 0x00); //

LPI2C1_Write(I2C_ADDR_ADC1, ADCX140_ASI_OUT_CH_EN, 0xf0);

LPI2C1_Write(I2C_ADDR_ADC1, ADCX140_IN_CH_EN, 0xf0);

LPI2C1_Write(I2C_ADDR_ADC1, ADCX140_PWR_CFG, 0x60);

// ADC 2 /////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

LPI2C1_Write(I2C_ADDR_ADC2, ADCX140_PAGE_SELECT, 0x00); // Set page to zero

LPI2C1_Write(I2C_ADDR_ADC2, ADCX140_SLEEP_CFG, 0x81); // Wake up and enable AREG

SysTick_Delay_ms(10);

LPI2C1_Write(I2C_ADDR_ADC2, ADCX140_ASI_CFG0, 0x20);

LPI2C1_Write(I2C_ADDR_ADC2, ADCX140_ASI_CFG1, 0x00);

LPI2C1_Write(I2C_ADDR_ADC2, ADCX140_ASI_CFG2, 0x80); // Set up for Daisy Chain Mode

LPI2C1_Write(I2C_ADDR_ADC2, ADCX140_ASI_CH1, 0x00); // Mapped to default slots

LPI2C1_Write(I2C_ADDR_ADC2, ADCX140_ASI_CH2, 0x01); //

LPI2C1_Write(I2C_ADDR_ADC2, ADCX140_ASI_CH3, 0x02); //

LPI2C1_Write(I2C_ADDR_ADC2, ADCX140_ASI_CH4, 0x03); //

LPI2C1_Write(I2C_ADDR_ADC2, ADCX140_GPIO_CFG0, 0xB0); // Make GPIO input for daisy chain

LPI2C1_Write(I2C_ADDR_ADC2, ADCX140_BIAS_CFG, 0x60); //

LPI2C1_Write(I2C_ADDR_ADC2, ADCX140_CH1_CFG0, 0x80); // Channel 1 configuration

LPI2C1_Write(I2C_ADDR_ADC2, ADCX140_CH2_CFG0, 0x80); // Channel 2 configuration

LPI2C1_Write(I2C_ADDR_ADC2, ADCX140_CH3_CFG0, 0x80); // Channel 3 configuration

LPI2C1_Write(I2C_ADDR_ADC2, ADCX140_CH4_CFG0, 0x80); // Channel 4 configuration

LPI2C1_Write(I2C_ADDR_ADC2, ADCX140_DSP_CFG0, 0x00);

LPI2C1_Write(I2C_ADDR_ADC2, ADCX140_ASI_OUT_CH_EN, 0xf0);

LPI2C1_Write(I2C_ADDR_ADC2, ADCX140_IN_CH_EN, 0xf0);

LPI2C1_Write(I2C_ADDR_ADC2, ADCX140_PWR_CFG, 0x60);

Can anyone give me any hints on why I would be getting intermittent samples that are sticking to all 0's or 1's? And only the first channel of the second ADC?

Thank you in advance everyone!