Hi, TI expert

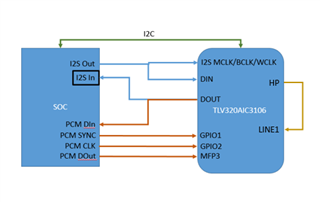

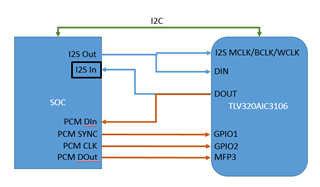

I am planing to use the TLV320AIC3106 to test I2S Out/In and PCM Out/In interfaces of the SOC with a loopback mode. The testing concept is below.

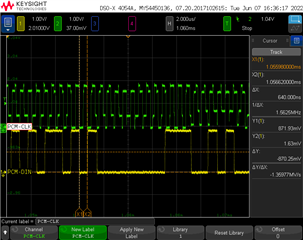

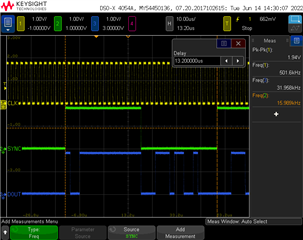

Now we are focusing on the PCM Out/In interface (I2S interface is ignored). My problem is the we can see the signal waveform at PCM SYNC, PCM CLK, and PCM DOut with a scope, but we do not see the signal waveform at PCM DIn. My initial code is below. I believe the initial code should have some problems. May I have your review and comments? Thank you!

function codec()

{

if [ ! -d /sys/class/gpio/gpio${codec_rst_pin} ] ; then

echo ${codec_rst_pin} > /sys/class/gpio/export

fi

echo out > /sys/class/gpio/gpio${codec_rst_pin}/direction

echo 1 > /sys/class/gpio/gpio${codec_rst_pin}/value

sleep 1

echo "PCM Test Mode"

i2cset -f -y $codec_i2c_bus $codec_addr 0x01 0x80 b

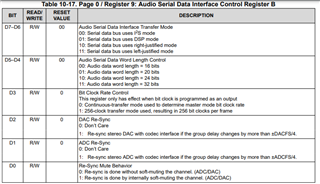

i2cset -f -y $codec_i2c_bus $codec_addr 0x07 0x8A b

# GPIO1 = word clock for audio serial data bus (programmable as input or output)

i2cset -f -y $codec_i2c_bus $codec_addr 0x62 0xB0 b

# GPIO2 = bit clock for audio serial data bus (programmable as input or output)

i2cset -f -y $codec_i2c_bus $codec_addr 0x63 0x80 b

# MFP3 pin usage as audio serial data input pin is enabled (MOSI)

i2cset -f -y $codec_i2c_bus $codec_addr 0x65 0x10 b

i2cset -f -y $codec_i2c_bus $codec_addr 0x08 0xC0 b

i2cset -f -y $codec_i2c_bus $codec_addr 0x29 0x02 b

i2cset -f -y $codec_i2c_bus $codec_addr 0x2B 0x00 b

i2cset -f -y $codec_i2c_bus $codec_addr 0x25 0xD0 b

i2cset -f -y $codec_i2c_bus $codec_addr 0x40 0x80 b

i2cset -f -y $codec_i2c_bus $codec_addr 0x2F 0x80 b

i2cset -f -y $codec_i2c_bus $codec_addr 0x33 0x0D b

i2cset -f -y $codec_i2c_bus $codec_addr 0x41 0x0D b

}

BR

Kevin