Hi Team,

I have asked a question related to MCLK, but that question chain got closed. i want to continue that discussion here, please help me to find out the cause.

Yes, we need to get MCLK from master side, we are able to get the MCLK 12.288MHz from QCS610(Master), but we are unable to hear any sound from Jac which is connected via TLV codec.

Previously we thought like, the MCLK is only the issue for not hear anything from audio jack. but now we are able to get mclk bclk data line everything as we configured from software side. but we not even hear any noise from audio jack

Please help us to find the cause,

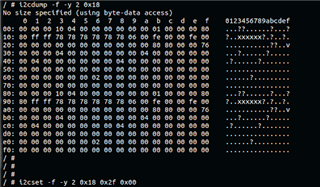

And as you asked earlier , have attached the i2cdump output.