We are going to use PCM1865 in slave clocking mode, w/o SCK.

Our target sample frequency would be a multiple of 52.1kHz. This is outside the dedicated sample frequencies listed on table 11 (chapter 9.3.9.4.4 BCK Input Slave PLL Mode) and it's also outside the sample frequency ranges shown for register at address 0x73 (page 0) within the datasheet (32..48kHz,88,2..96kHz, 176,4..192kHz).

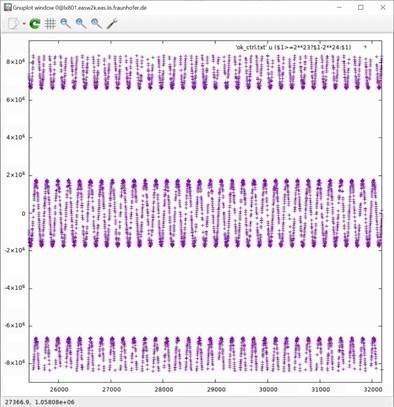

We tried to use a BCK ratio of 48 (LRCK=52,1kHz, BCK=2,5MHz) and a BCK ratio of 64 (LRCK=52,1kHz, BCK=3,334MHz). Both without success (sufficient sample values on the I2S output). Could the PCM1865 work using this setup?

Many thanks + best regards.