Hello,

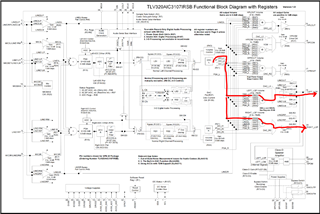

Our customer is evaluating TLV320AIC3007 ADC noise include analog PGA function.

We have two concern, first one is "noise floor vs PGA gain" is changed not linear response.

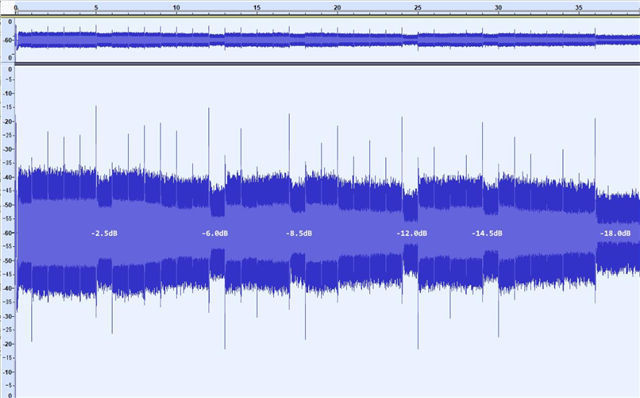

Attached waveform is noise floor level when change PGA level from 0dB to -16dB by 0.5dB step from left side to right side.

You can see -6dB point is lower noise floor than -5.9dB(one left) or -6.5dB(one right).

A-WTD reading value is -90dBu at -6dB and -86dBu at 5.9dB and -6.1dB

Similar response we can see at -2.5dB, -8.5dB, -12dB, -14.5dB and -16dB.

What is reason of this noise variation?

Is it come from PGA feedback network resistor value? At some point use high resistance.

Or analog PGA and Digital attenuator hybrid volume topology is used?

Second one is zipper noise, each 0.5dB step create zipper noise as you can see the waveform.

Is there any way to improve this zipper noise at no signal input condition?

It is not talking about zero-cross switching scheme. But might be DC offset of PGA.

Regards,

Mochizuki