hi team:

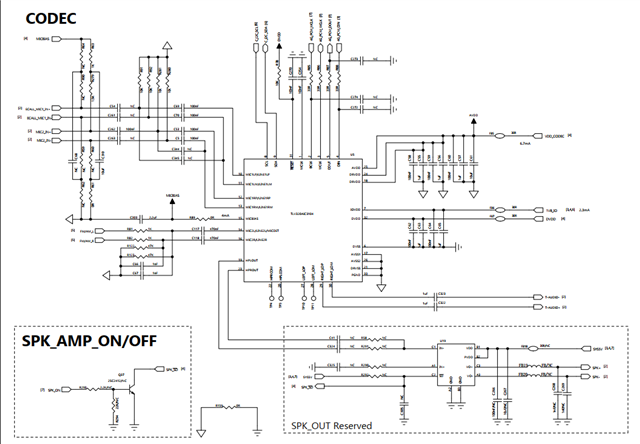

we are using the TLV320AIC3104 to output a stable sound signal on RIGHT_LOM/LOP. Now RIGHT_LOP has sound output, and RIGHT_LOM has no sound output. I follow the documentation instructions as below:

1.D7 of Register 89 and Register 92 is routed to DAC_L1/R1 stereo channel to RIGHT_LOP/LOM. By default, D7 of Register 92 is set to 1.

2. Register 89 is set to 1, RIGHT_LOM still has no sound.

If there are any registers to pay attention to? tks for you support!