I'm trying to operate the TLV320AIC3101 in the following configuration and I'm having difficulty confirming if my registers are set up correctly. Could someone look at my settings and let me know what is wrong?

- 48 kHz sample rate

- No PLL

- CLKDIV_IN source from BCLK

- DAC fs/1

- Microphone input on MIC1RP/MIC1RM to DOUT

- DIN input to HPLOUT and HPROUT

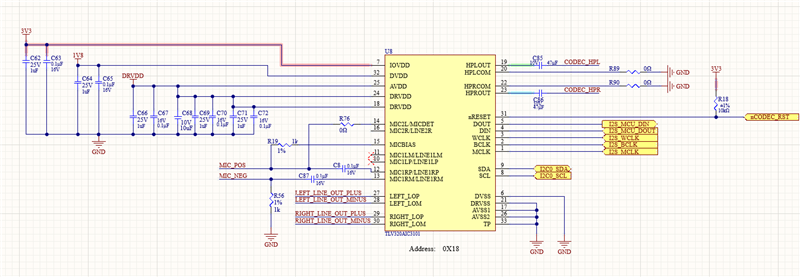

Here is the schematic:

I have my hardware setup where I'm playing a ~400 Hz 0.5 Vpp sinewave into MIC1RP and MIC1RM inputs. The codec does AtoD on the sinewave and sends it to the host MCU via I2S. The MCU echos back the I2S data and the codec and plays the output. I can hear the output on the headphones, but it's very quiet. I've tried a few different gain settings but I'm not sure which one I should be looking at first.

Here are my register settings:

static const codecValues defaultRegisterMap[] = {

0x02, 0x00,

0x04, 0x04,

0x05, 0x00,

0x06, 0x00,

0x07, 0x0A, // 48 kHz fs, Left-DAC plays left channel input data, right-DAC plays right channel input data

0x08, 0x00,

0x09, 0x00,

0x0A, 0x00,

0x0B, 0x01,

0x0C, 0xF0, // Enable high pass filter for Left ADC and Right ADC

0x0D, 0x00,

0x0E, 0x80, // AC coupled high power output, psueo differential output

0x0F, 0x00, // Left ADC PGA gain of 0 dB

0x10, 0x3F, // Right ADC PGA gain of ~30 dB

0x11, 0xFF, // Disconnect MIC2L/R from left ADC

0x12, 0xFF, // Disconnect MIC2L/R from right ADC

0x13, 0x78, // Left ADC powered down. LINE1L not connected to left-ADC PGA. We only have input on the right ADC

0x14, 0x78, // Left Channel Analog Inputs to CM connection

0x15, 0xF8, // MIC1RP to Left-ADC Control Register. MIC1RP differential mode. LINE1R is not connected to left ADC.

0x16, 0x84, // MIC1RP to Right-ADC Control Register. Right ADC powered up, differential microphone mode, -0 DB volume

0x17, 0x78, // Right Channel Analog Inputs to CM Connection

0x18, 0xF8, // LINE1L not connected to right ADC

0x19, 0x80, // MIC bias selection. Disable bias = 0x00, AVDD is 0xC0, 0x40 is 2.0V, 0x80 is 2.5V

0x1A, 0x00, // Left-AGC control register

0x1B, 0x7F,

0x1C, 0x00,

0x1D, 0x00,

0x1E, 0x7F,

0x1F, 0x00,

0x20, 0x00,

0x21, 0x00,

0x22, 0x00,

0x23, 0x00,

0x24, 0x00,

0x25, 0xE0, // Left DAC powered up, Right DAC powered up, HPLCOM is independent single-ended output

0x26, 0x14, // HPRCOM is independent single-ended output, Short-Circuit Protection is enabled

0x28, 0x00,

0x29, 0xA0, // Left and right DAC output path selects path 2

0x2A, 0x38, // Output driver pop reduction

0x2B, 0x10, // Left-DAC digital volume control register

0x2C, 0x10, // Right-DAC Digital Volume Control Register

0x2E, 0x00, // PGA_R is NOT routed to HPLCOM

0x2F, 0x00, // DAC_L1 is NOT routed to HPROUT

0x31, 0x00,

0x32, 0x00,

0x33, 0x0D, // HPLOUT output level control to 0 dB.

0x35, 0x00,

0x36, 0x00,

0x38, 0x00,

0x39, 0x00,

0x3A, 0x0C, // HPLCOM Output level control register

0x3C, 0x00,

0x3D, 0x00,

0x3F, 0x00,

0x40, 0x00,

0x41, 0x0D, // HPROUT output level control to 0 dB.

0x43, 0x00, // PGA_L is NOT routed to HPROUT

0x44, 0x00,

0x46, 0x00,

0x47, 0x00,

0x48, 0x0C, // HPRCOM Output level control register

0x51, 0x00,

0x52, 0x00,

0x54, 0x00,

0x55, 0x00,

0x56, 0x00,

0x58, 0x00,

0x59, 0x00,

0x5B, 0x00,

0x5C, 0x00,

0x5D, 0x02,

0x5E, 0x00,

0x5F, 0x00,

0x65, 0x01,

0x66, 0xA2,

0x67, 0x00,

0x68, 0x00,

0x69, 0x00,

0x6A, 0x00,

0x6B, 0x00,

0x6C, 0x00,

0x6D, 0x00,

};

This is the audio path I am trying to achieve:

Can someone let me know if my settings are wrong?

Thanks.