Hi,

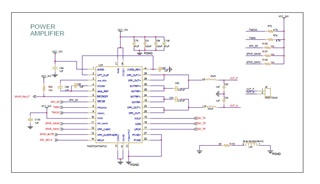

We are using TI's Automotive Class-D Audio Amplifier 'TAS5720ATDAPQ1' and the controller we are using is ATMEL's 'ATSAMV70Q20B-AAB'.

The audio output is not generating even though we are able to generate all I2S clks with following frequencies and proper clock ratios..

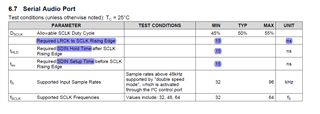

Sampling Rate: 48 KHz

Internal SSC MCLK for Generating TK & TF: 150000000

MCLK: 12.28 MHz

Bit CLK (TK): 1.53 MHz

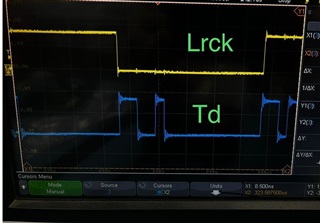

Word CLK (TF): 48.00 KHz

Data (TD): data - 16 Bit

Bit CLK to word CLK Ratio: 32 (even we tried with 64)

We observed that bit 'CLKE' is getting set in Fault register (0x08, value: 0x08) indicating the 'non-latching intermittent clock error'.

We also observed that the fault pin pulsing continuously (low for 10us with every 350us gap).

After power on and reading fault register we tied toggle the SPK_SD pin and tied tied this to SPK_FAULT pin, but even this doesn't help.

Please let us know whether this error (CLKE bit set) is generating for improper clock ratios or any distortion/delays in the clocks.

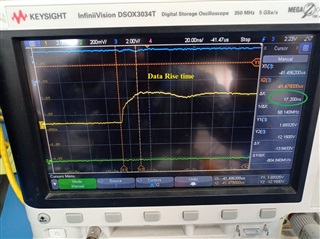

The snapshot of the schematics section of amplifier is attached for your reference. Also attached few of the i2s clock/data waveforms.

Regards,

Imran,

mJm Technologies, Bangalo

re

re