Hello All!

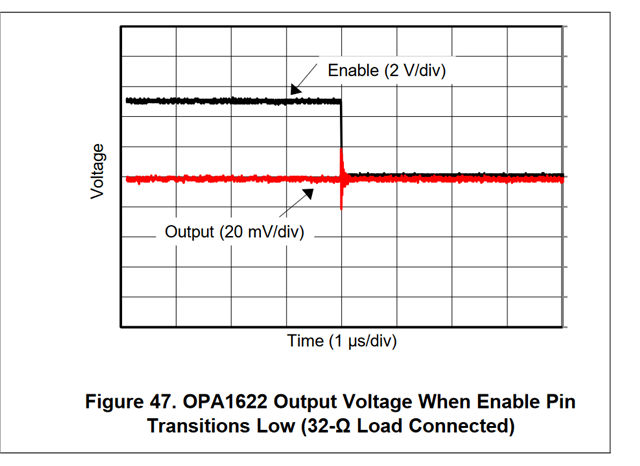

I'm experiencing a very odd behavior when trying to use the enable pin feature of the OPA1622 in the clipper circuit below:

As can be seen above, I'm setting the GND pin to -9V in order to reference the enable signal to it.

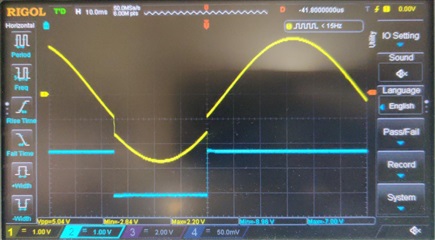

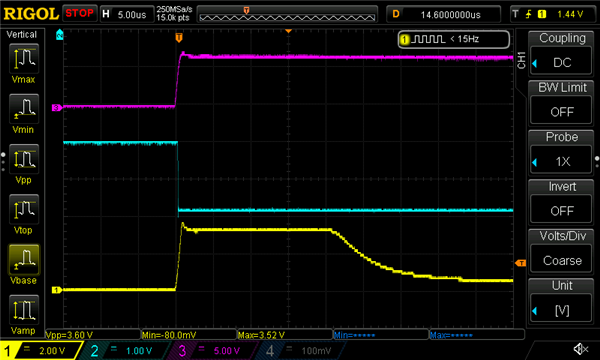

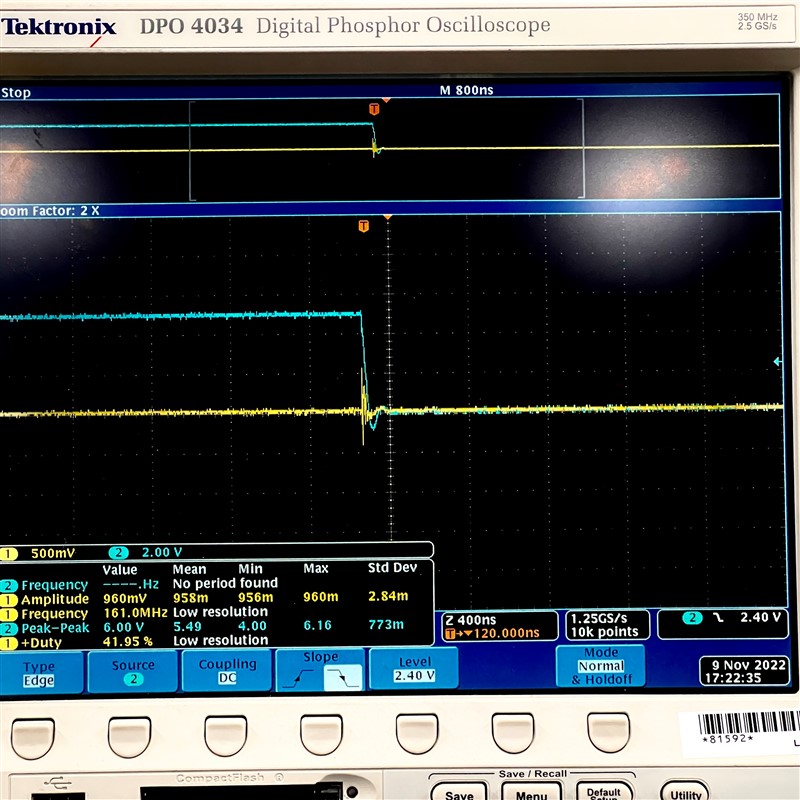

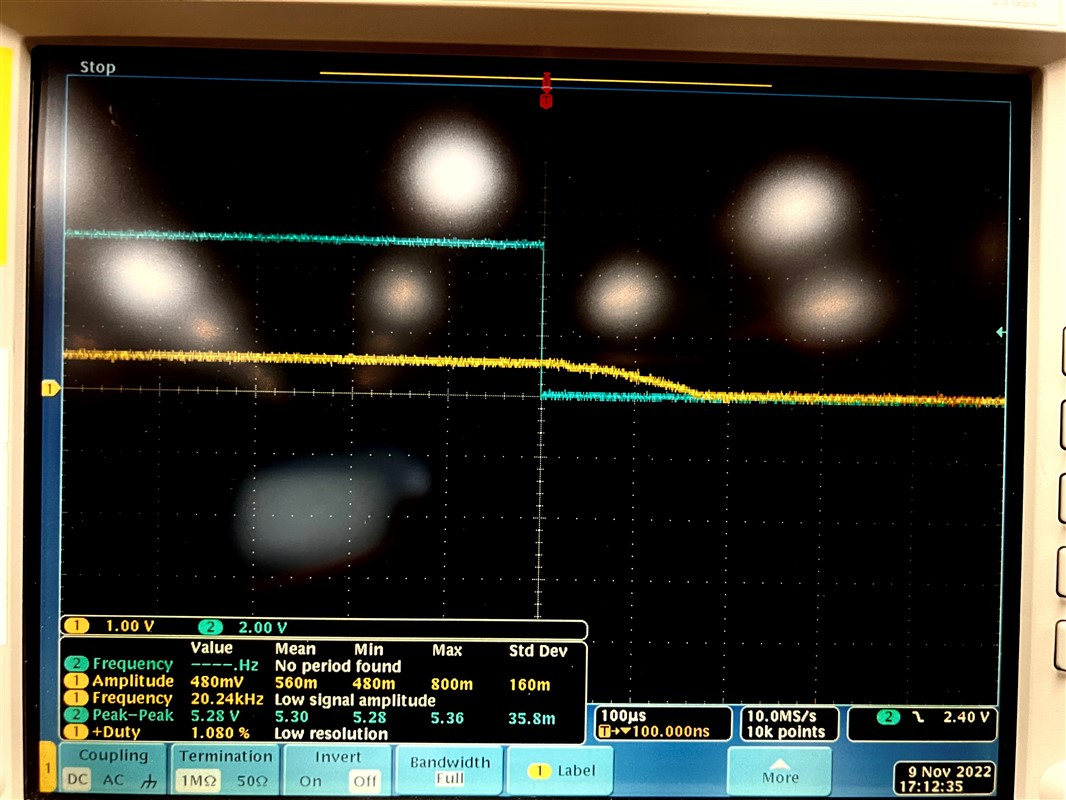

The enable signal generation (in cyan below) mechanism works as expected, but the OPA1622 output (in yellow below) does not:

I should also mention that I'm using 2 diode in series to protect the power supplies from inverting.

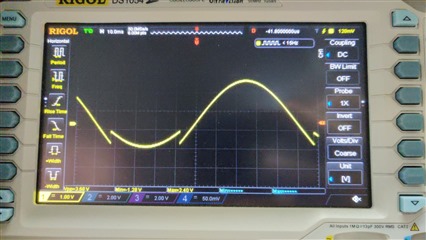

I'm a bit at a loss :) .