Dear E2E Support,

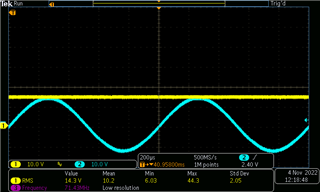

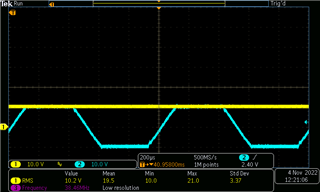

Folowing the datrasheet details, the PVDD Foldback feature doesn't need to be fine tuned. Everything is automatic, through the register DSP_CTRL2 (Address = 0x3A).

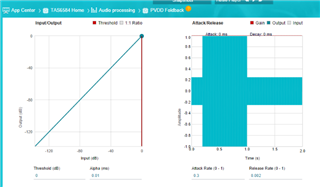

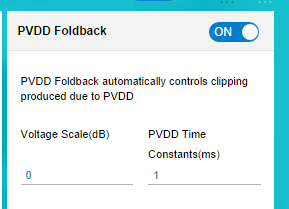

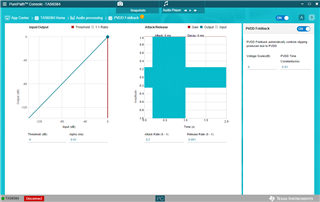

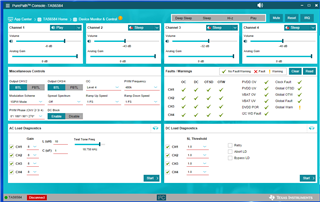

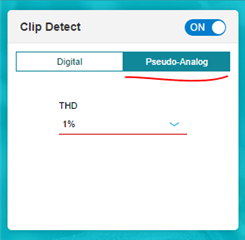

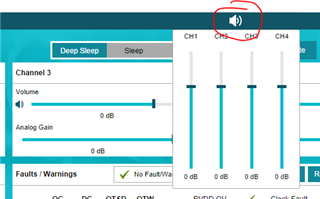

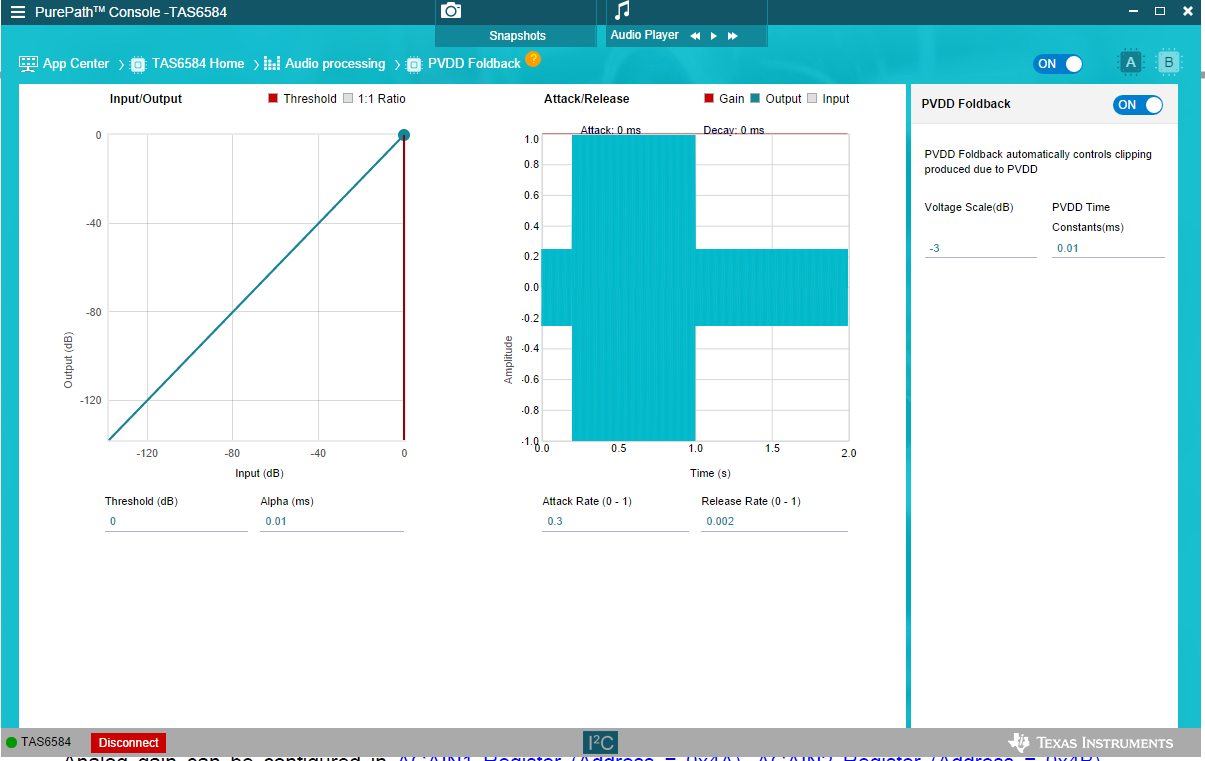

In PCC3 we have a dedicated section to PVDD foldback, where several parameters are settable.

Could you explain all these options?

Regards,