Other Parts Discussed in Thread: PCM5102, DIX4192, SRC4392, PCM5100, TLV320ADC3120

I am designing a circuit which has;

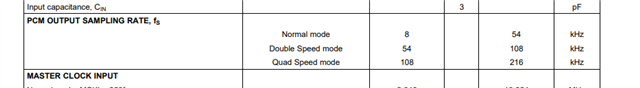

ADC = PCM4220, system clock is 64*Fs, operates in slave mode

DAC = PCM5102, system clock is 128*Fs

Requirement is they both need to be 200kHz (Fs). However, the PCM4220 requires 12.8MHz and PCM5102 requires 25.6MHz.

The processor is being clocked at 25.6MHz but it cannot generate the 12.8MHz clock for the ADC so I am using the IDT 5P49V6913 programmable oscillator to generate the 25.6MHz (DSP & DAC) and 12.8MHz (ADC). The processor will be generating the ADC L/R clock and bit clock.

Does the ADC master clock need to be phase locked (edge aligned) to the left-right clock and bit clock?