hi team:

My customer reporting the MIC2R(pin16) can not collect the audio signal, meanwhile the PIN14 of MIC2L is workable ,here is my primary checking list with my customer ,can you help to take a look and give your professional comments? tks in advance!

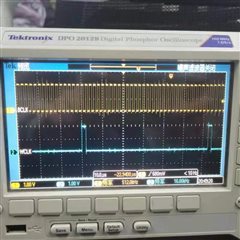

here attached the register file ,you may check the MIC2R page for your reference.

11-25 AIC3104 config list.xlsx

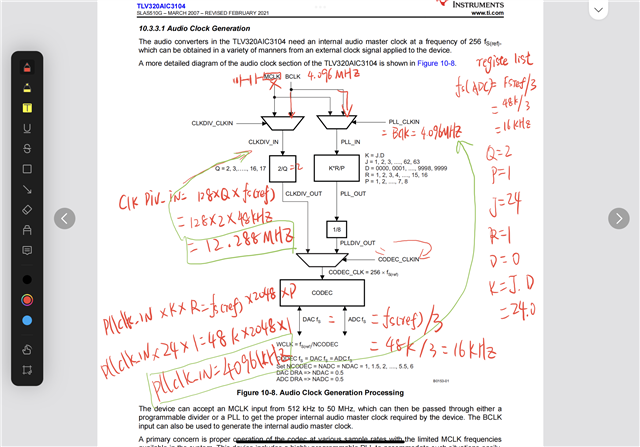

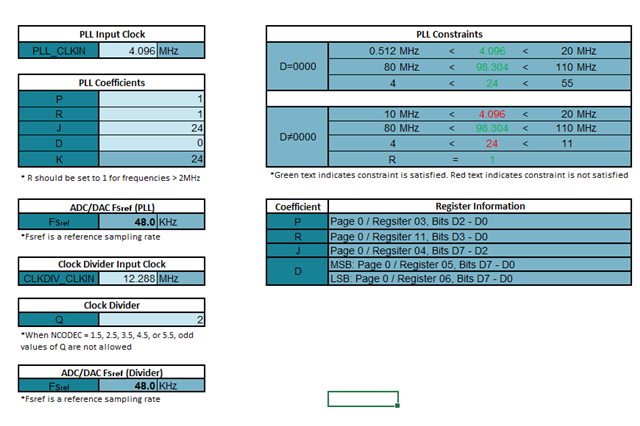

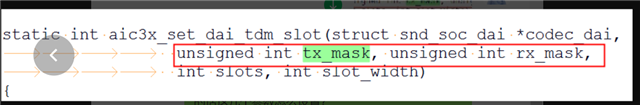

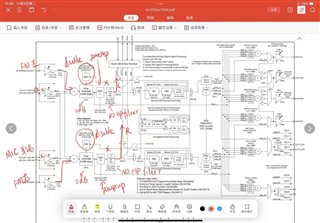

here attached my understanding corresponding to the register list.

here attached the customer system block diagram:

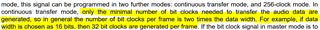

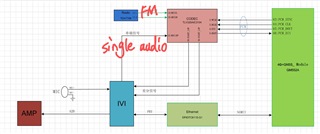

here also attached another hardware test from the customer side:

-> The audio source comes from 3.5mm headphone to PIN16 and 14.

There are three connection methods:

1. Normally ,audio R to PIN16 and L to PIN14.

2. Swap left and right and L to PIN16 and R to PIN14.

3. Both of the above two results ensure that there is an audio signal entering PIN16, but neither can have stereo output。(R audio missing)

->Impedance measurement test:

1.use the multimeter diode channel(red pen to ground, black pen to chip pin) measurement results: PIN16 is 0.440, PIN14 is 0.463;

2.use the multimeter resistance channel(red pen to chip pin , black pen to ground) measurement results: PIN16 is 6.6M, PIN14 test is 6.6M;

according the above test, i think the hardware part is okay, can you help to comment? tks !