Other Parts Discussed in Thread: PCM5122

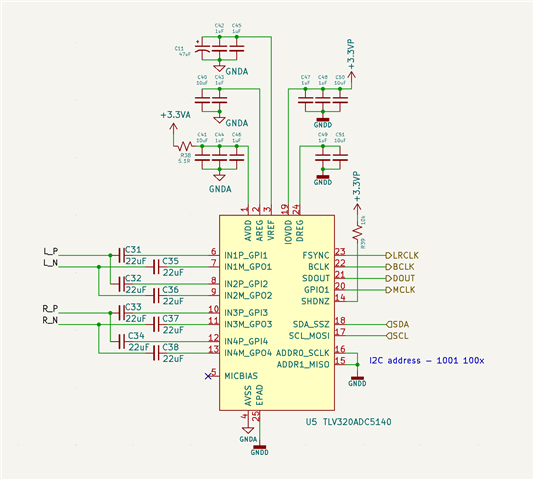

We're attempting to test TLV320ADC5140 in I2S master mode and by our understanding, supplying mclk was optional. Out PCB has a pad for a single 24.576mhz crystal as we only operate in 48khz-related sample rates. Currently, the XO is unpopulated. Our understanding was that the TLV320 could supply its own internal BCK and LRCK outputs however given the sequence below we get no I2S BCK/LRCK. Here is the schematic:

We attempted to activate with this sequence (pseudocode, using node.js and i2c library, registers are being written as confirmed below):

const MST_CFG1_RATES = {

48 : 0x48, // 01001000

96 : 0x58, // 01011000

192: 0x68, // 01101000

384: 0x78 // 01111000

};

// SLEEP_CFG wake

await i2cWriteByte(0x02, 0x91);

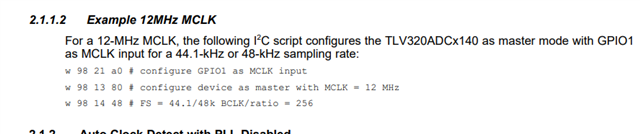

// MST_CFG0 master, 48k 10000111

await i2cWriteByte(0x13, 0x87);

// i2cWriteByte(0x16, 0xXX); // CLK_SRC master (not using for now)

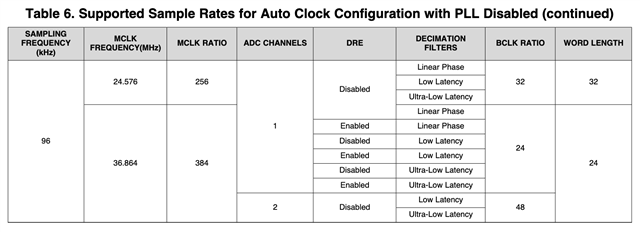

// 256x 96k, 01011000

await i2cWriteByte(0x14, MST_CFG1_RATES[96]);

// ASI_CFG0 i2s, 32bit, 01110000 ? (not sure about last two bits)

await i2cWriteByte(0x07, 0x70);

// DSP_CFG sum pairs 00000100 ? not sure about HP

await i2cWriteByte(0x6B, 0x04);

// DEV_STS0 power up 1-4? 11110000

await i2cWriteByte(0x76, 0xF0);

// IN_CH_EN enable input 1-4? 11110000

await i2cWriteByte(0x73, 0xF0);

// ASI_OUT_CH_EN enable 1,2? 11000000

await i2cWriteByte(0x74, 0xC0);

// CH1_CFG0 config input, line, single-ended, no dre, 20k: 10101000

await i2cWriteByte(0x3C, 0xA8);

// CH2_CFG0

await i2cWriteByte(0x41, 0xA8);

// CH3_CFG0

await i2cWriteByte(0x46, 0xA8);

// CH4_CFG0

await i2cWriteByte(0x4B, 0xA8);

Confirmed values with i2c read and got:

{

'0x02': '10010001',

'0x13': '10000111',

'0x14': '1011000',

'0x07': '1110000',

'0x6B': '100',

'0x76': '0',

'0x73': '11110000'

}

0x76 does not seem set. We still expected to see signs of life on FSYNC and BCLK. Is the XO input required on GPIO1? The datasheet made it seem optional so we wanted to test performance without it. In addition, this I2S master is the master to our PCM5122 on the same board. Haven't gotten that far, though.