Other Parts Discussed in Thread: TAS6424,

Hi Team,

When customers use TAS6424, they use TDM signal. After they change MCLK from 12.288MHz to 24.576MHz, there is no sound.

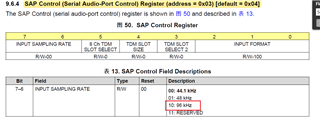

According to the Datasheet, I think the ratio of FSYNC, MCLK and SCLK does not meet the requirements, as follows:

At this time, in addition to modifying the frequency of FSYNC in the SAP register to 96kHz, what else do we need to do?

How should 256xFs be configured?