Hello there,

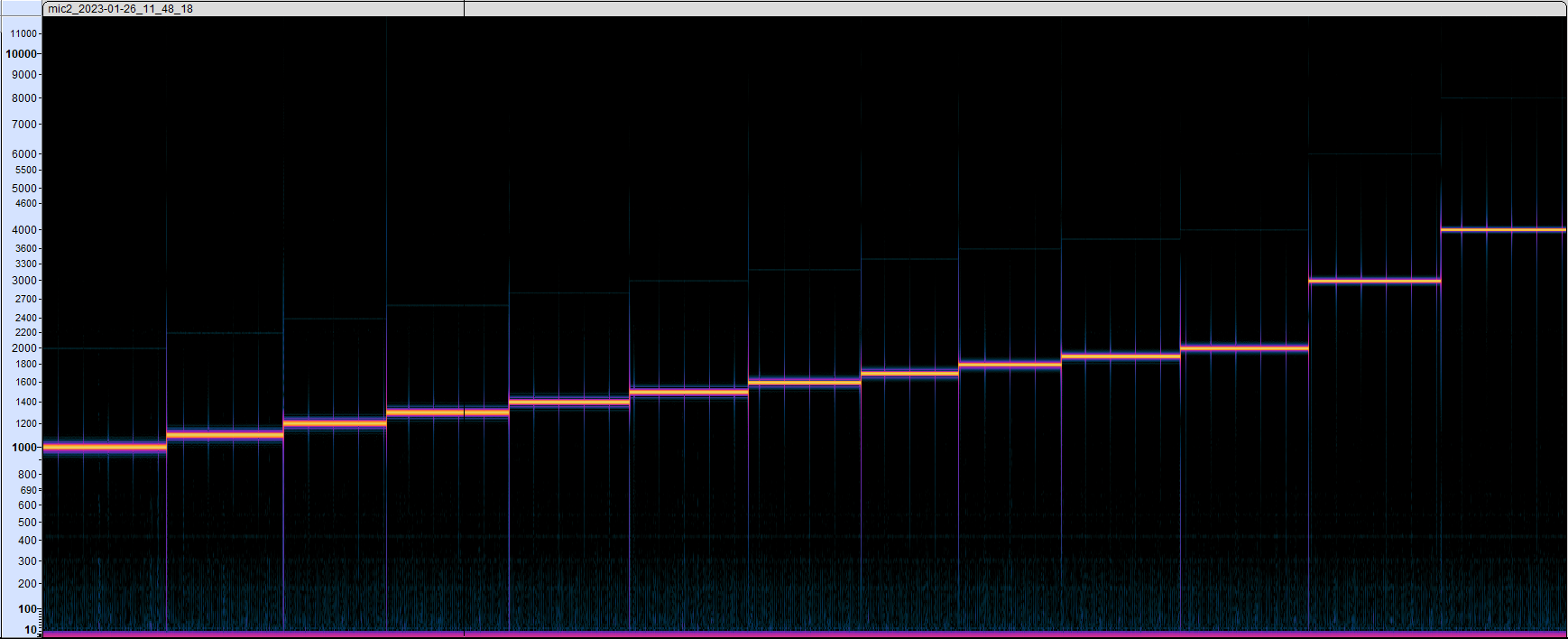

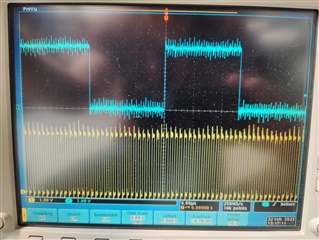

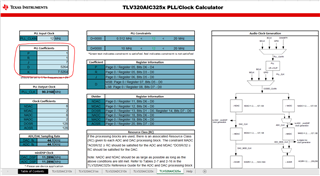

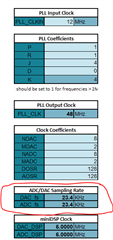

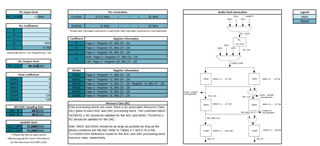

I am experiencing a peculiar issue with a TLV320AIC3254 audio codec that is interfacing with a Raspberry Pi CM4 via I2C and I2S on a carrier board of our own design. We are recording audio from two microphones connected differentially to IN1_L/R and IN2_L/R respectively. We have tested this unit extensively, and audio recording works reliably and well. However, our end user complained about an audible clicking sound that occurs roughly every 1.3 seconds throughout any recording. They did a test recording using a microphone, and a frequency generator outputting a sine wave through a speaker that swept through a range of frequencies. To replicate this problem, we performed a similar test with an arbitrary waveform generator outputting a 100mV-amplitude sine wave directly into the codec's secondary input as a line-in signal. During this test, I started at 1KHz, and stepped up the frequency at 100Hz intervals until I reached 2KHz; then stepped it to 3KHz and finally 4KHz. As can be seen in the attached spectrogram, we are getting consistent clicks approximately every 1.3 seconds regardless of what frequency is used.

Oddly, in further tests, the timing of the clicks appears to be affected by the latency or block size, but only at the 44.1kHz sample rate. Normally we are running at a 48kHz sample rate, and adjusting latency or block size doesn't seem to change the timing.

Any thoughts of how to mitigate this issue would be greatly appreciated.

Thanks!