Other Parts Discussed in Thread: PCM1821

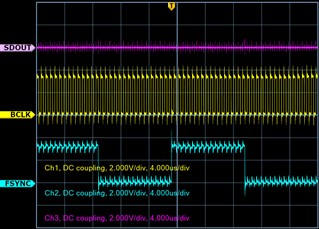

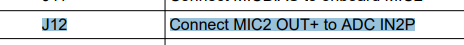

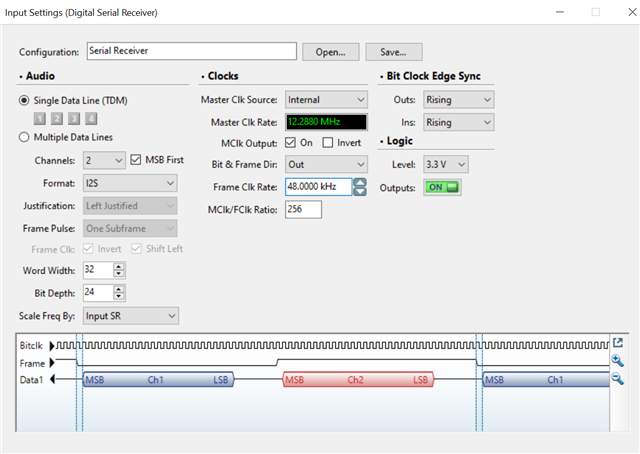

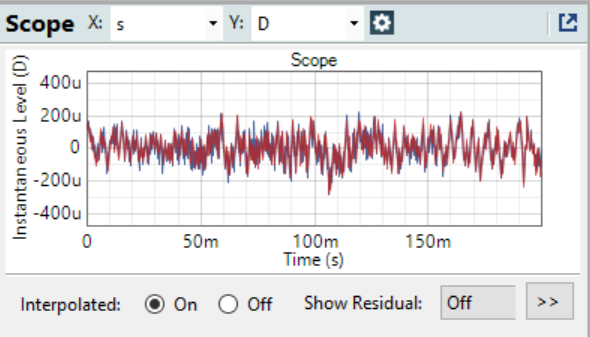

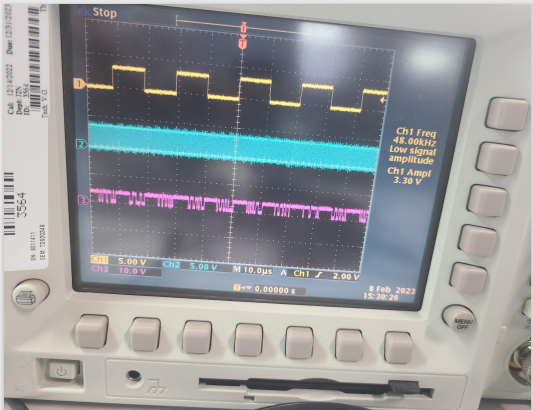

I'm having trouble getting any output from the SDOUT pin of my PCM1821EVM. I have the jumpers inserted according to Figure 4-2 for Onboard Microphones. I have the J5 jumper selecting 3.3V for IOVDD, J4 selecting AVDD for MPWR. J9 & J10 inserted, passing 3.3V to AVDD and IOVDD, I have the configuration jumpers all set to 0 (J12, J17, J18, and J20) for slave mode. I believe my BCLK and FSYNC signals are good, as shown in the attached waveform capture. However, I don't ever see any non-zero data on SDOUT. In the attached waveform I'm probing at the green testpoints for FSYNC, BCLK, and SDOUT. I've confirmed that there is at least some signal on IN1P and IN1M, so I don't believe the failure to get non-zero SDOUT data is due to lack of signal. Suggestions? Thanks in advance.