Part Number: PCM1754

Hi experts:

As the datasheet of PCM1754, its I2S interface is right-justified. And this part support 16bit to 24bit of data. My question is how the device know where is the MSB?

Thank you!

John

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi John,

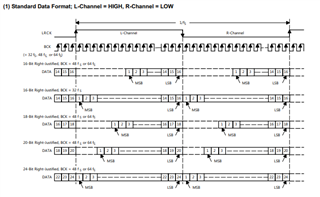

Since it is right justified, your data pack will be aligned as right justified, so it takes the last bit of the pack in the frame as LSB and moves toward MSB, once it is done, it will pad with zeros to fill out the whole frame as 24 bit.

Please refer to the below diagram.

Regards,

Arash

Hi Arash,

Thank you for reply.

Yes i understand it is right justified. But my question is, there is only one pin 'FMT' for data format configuration. As "Table 2. Data Format Select", in page 17 of PCM1754 datasheet, the I2S data format could be 16- to 24-bit when FMT is low. While there is not other pin telling device what is the exact word length. So how does device know the actual data word length? Additionally, the data is 16- to 24-bit when FMT is configured low, and 16-bit when FMT is high, seems this is a redundant configuration, why?

Regards,

John

Hi John,

The frequency of BCLK is calculated using the following equation: BCLK=#of channels * fs * Bit depth for channel

So once you have the frequency of both clks along with number of channels ,, the bit depth is known.

For example if you are using a BCLK of 1.536MHZ and Fs of 48K with 2 channels, the bit depth for each will be calculated to be 16

Also FMT tells the device if the format is I2S (L) or Right Justified (H), nothing redundant.

Regards,

Arash

Hi Arash,

Thank you.

Your explain seems does not match the datasheet description. Based on datasheet i think the BCLK frequency is flexible.

I read the datasheet in detail again, here is my understanding, please help me check if it is truth: Maybe I confused I2S format and standard format. FMT low means data format is I2S format in stead of standard format, and FMT high means standard data format. I2S data format is in fact left justified but MSB start from second BCLK rising edge (Fig 23, "(2) I2S Data Format; L-Channel = LOW, R-Channel = HIGH"). BCLK can be 48fs or 64fs, sample data can be 16- to 24-bit. Customer should pad with zeros after LSB of data if the bit depth lower than 24bit. The device itself always take 24bit of data for conversion, so it does not need to know what bit depth is using. If this understanding correct?

Regards,

John

Hello John, basically the difference b/w left justified and I2S is the one clock cycle of BCK location of data as you notice. The device expect to receive 24bit data and the FMT fin tells the format of I2S or left justified will be applied. The equation that I gave you is a universal equation that governs the relationship b/w frequencies of Fs, BCK and # of channels and the resulted BCLK. For a a given Fs and # of channels, if you change the word length, BCLK will change accordingly . If you have access to AP you can see this in Interface Receiver window and can play with these parameters and notice how BCLK changes accordingly.

In general you don't need to tell the device the word length . I think we are on the same page.

Regards,

Arash