Hi,

1) Our TLV320AIC3100 is connected to STM32F4 MCU with SAI configured as I2S. DIN => DAC => speaker is producing proper sound without any noticeable artifacts. MIC => ADC => DOUT however is producing rubbish and I can barely make sense what has been sampled. To debug this problem, I enabled DIN to DOUT loopback and disabled MIC & speaker. After inverting BCLK (page 0, register 29, bit 3), DOUT data started to look somewhat similar what was fed to DIN.

Here's a register dump. Rest of the registers are unmodified.

PAGE..ADDR..VALUE..|7|6|5|4|3|2|1|0|

0.....011...129....|1|0|0|0|0|0|0|1|

0.....012...130....|1|0|0|0|0|0|1|0|

0.....013...000....|0|0|0|0|0|0|0|0|

0.....014...128....|1|0|0|0|0|0|0|0|

0.....018...129....|1|0|0|0|0|0|0|1|

0.....019...130....|1|0|0|0|0|0|1|0|

0.....020...128....|1|0|0|0|0|0|0|0|

0.....027...000....|0|0|0|0|0|0|0|0|

0.....028...000....|0|0|0|0|0|0|0|0|

0.....029...040....|0|0|1|0|1|0|0|0|

0.....037...000....|0|0|0|0|0|0|0|0|

0.....063...020....|0|0|0|1|0|1|0|0|

0.....064...012....|0|0|0|0|1|1|0|0|

0.....065...000....|0|0|0|0|0|0|0|0|

0.....081...128....|1|0|0|0|0|0|0|0|

0.....082...000....|0|0|0|0|0|0|0|0|

1.....032...006....|0|0|0|0|0|1|1|0|

1.....035...000....|0|0|0|0|0|0|0|0|

1.....038...127....|0|1|1|1|1|1|1|1|

1.....042...000....|0|0|0|0|0|0|0|0|

1.....047...000....|0|0|0|0|0|0|0|0|

1.....048...000....|0|0|0|0|0|0|0|0|

3.....016...130....|1|0|0|0|0|0|1|0|

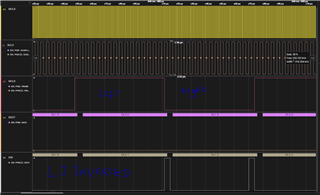

BCLK and WCLK frequencies.

Logic analyzer settings.

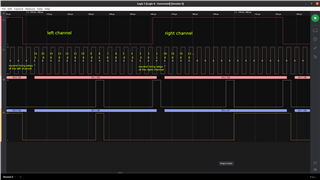

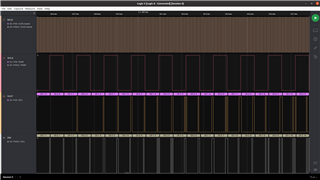

Feeding 1,2,3,4,5... to DIN and reading it back from DOUT. BCLK is inverted here. You can see that ch2 is (ch1 - 1) "behind". To me this seems like an alignment issue because on TLV320AIC3100 ch2 should equal ch1 (mono audio). Can you spot what's wrong?

2) Can TLV320AIC3100 generate master clock? For example if I enable PLL and set BCLK as a PLL_CLKIN, do I any longer need to feed MCLK from MCU to TLV320AIC3100? What I'm basically asking is can PLL serve as a substitute for MCLK?