Hello Experts,

My customer has question as follows. Would you answer it, please?

1. When /PDWN is toggled L to H, how much time is need to output from DOUT?

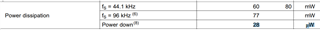

2. While device is power down mode and clocks are input, customer would like to know power dissipation of Icc and Idd. The datasheet stated only clock halt.

Best Regards,

Fujiwara

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.