Hi,

we're having some issues on some of our amplifier boards, where 10 out of 50 boards fail with FAULT pin going low. It seems like it is the DC protection that kick in, as we're measuring about 6.5v on one of the outputs (OUTPL/OUTNL) when the chip is in fault state and also when the chip is in disabled state (SDZ low) with no speaker connected.

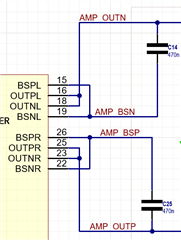

My question is how is the bootstrap capacitors expected to be connected in PBTL mode? In our current design we have doubled the capacitance (to 470nF), and connected BSPL and BSNL together as shown in the below snippet. Is this okay, or should BSP and BSN inputs have their own capacitor? Could this be the reason for the failures, or should it be okay?

BR

Vidar