Hi, TI support team

The customer encountered the following problems while using the product.

[problem]

- Product dead (burned, product destroyed), PVDD and GND short, Audio output ch and GND short

[condition]

- output power : 130~140W

-Load : 2ohm

[inquiry]

Due to a problem with some products, we plan to request a defect analysis.

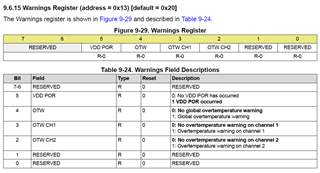

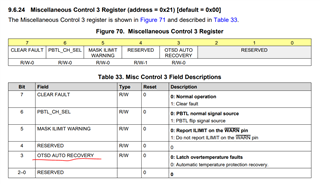

1. Overcurrent shut-down

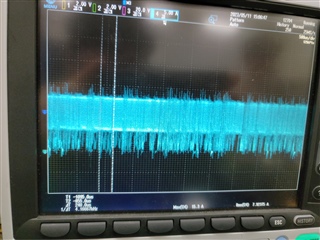

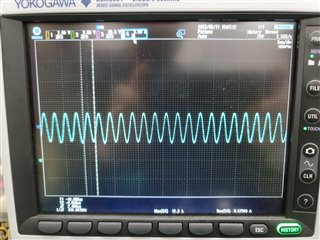

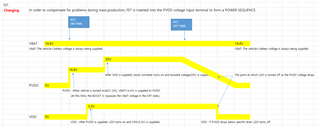

The waveforms below are in normal operation, and the WARN pin, FAULT pin, and Audio output were measured while increasing the output power (current).

(Normal operation, 4A, WARN high, FAULT high)

(Normal operation, 7A, WARN low, FAULT high)

(Normal operation, 7A, WARN low, FAULT high)

As the current increases, the WARN pin operates from high to low, but the FAULT pin does not operate despite increasing the power to 15A.

Why doesn't the FAULT pin work?

Is it normal that it doesn't work?

The cause of the above problem (IC burned) is expected to be caused by overcurrent, but are there other causes?

2. Overtemperature shut-down

Thermal information is not described in detail in the datasheet.

The shut-down operation of the product is assumed by thermal protection.

A heatsink is applied, and the temperature of the heatsink is operating at 130 degrees.

In the condition below, please inform the operating junction temperature.

- Low temperature (-40 degree)

- Room temperature (25 degree)

- High temperature (60 degree)

Thanks.

Regards,

MJ