Part Number: SRC4382

Other Parts Discussed in Thread: SRC4392

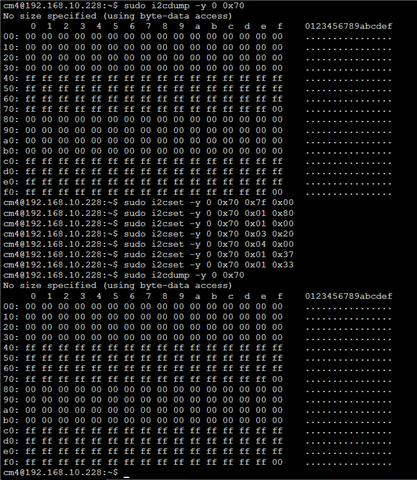

I've a strange issue on writing SRC4382 registers via I2C.

To configure the registers I'm using the i2c-tools application.

The first write is to the Page selection register 0x7f 0x00 (to configure control and status registers)

Reading back this register the value corresponds to the configured value (also if the page selection value is configured with a value different from 0x00)

After that I write the register 0x01 with 0x3F value to exit from power down status.

Reading back this register the value remains to 0x00.

This issue happens for all registers except the 0x7F and the 0x00 (that in datasheet is declared as reserved register).

Do you have an idea about the cause and what I can check?

I've looked at the I2C bus and seems that aren't any analog or protocol issue on I2C signals.

NB: the I2C bus runs at 40KHz.

Thanks