Hi team,

One of our customer's issues, could you please provide some troubleshooting suggestions?

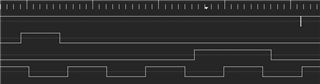

DIX4192 uses SPDIF's STATE bit to send and receive user data. Currently, data can be transmitted through SPDIF, but data cannot be received. Use oscilloscope capture can see the user data in STATE bit.

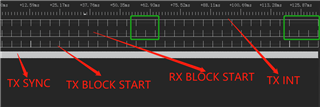

Configure GPO3 as RX BLOCK START,GPO2 as RX INT, and GPO1 as TX INT. Configure the corresponding register.

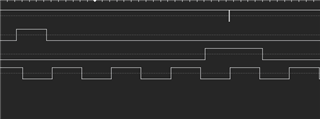

Open the interrupt of RBTI, receive the block start signal, set RXBTD to 1 after 2ms delay, wait for the interrupt of RBTI, read the user data and status register after entering.

The current issue is that the data sent by the main control board can be received, while the data sent by DIX4192 can occasionally be received by the main control board. What is the reason for this?

Is it possible that there is an issue with the block start timing? Start sending blocks according to this setting:

Best Regards,

Amy Luo