Hello,

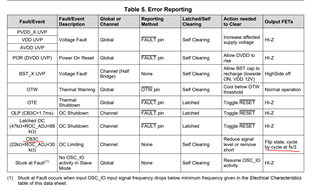

The datasheet for the TPA3255 states that the outputs will go into a Hi-Z state during Fault conditions. Based on Figure 26. it looks like the low side gate drive goes high, wouldn't this cause the outputs to pull down instead of going into hi-Z (Assuming NMOS halfbridge output). We are seeing leakage current into the output when in a fault condition and want to clarify if this behavior is expected.

Thanks.