Hi Team,

when I test the PCM5121EVM the delay time is not match with the datasheet descprition.

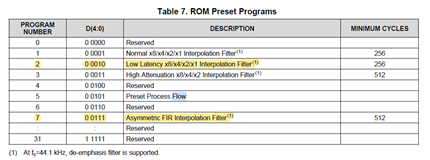

in datasheet the 0x02 preset flow delay time is 3.5/fs, when fs=48K, but the AP actual test DUT delay time result is 104.3us.

the 0x07 preset flow is 1.2/fs, when fs=48K, but the AP actual test result is 125.0us.

question:

1. what is the shortest delay time of the PCM5121?

2. why the 0x07 preset flow delay time is larger than 0x02 preset flow, why the delay result it not match with 3.5/fs or 1.2/fs.

Thanks.

Anderson