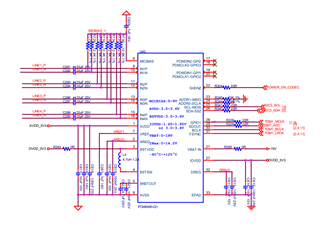

Part Number: PCM6480-Q1

Hi,

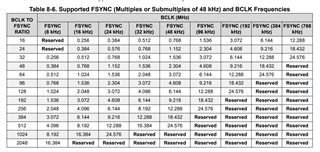

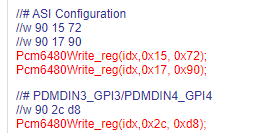

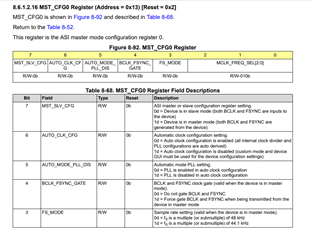

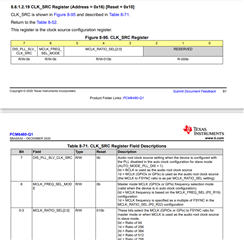

I am using PCM6480-Q1 in slave mode,Auto clock configuration is enabled,PLL is enabled in auto clock configuration,FS is a multiple (or submultiple) of 48 kHz.

BCLK input 24.576Mhz, FSYNC input 768Khz.

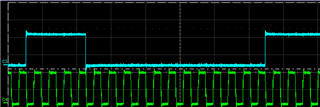

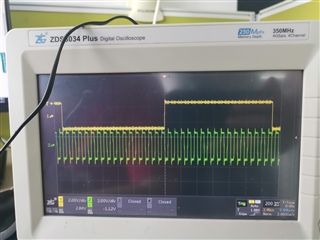

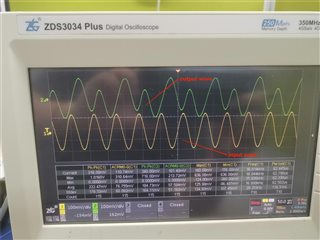

When I input 16Khz sine wave signal to IN1, the output signal will be distorted after sampling, as you can see below:

BCLK input 12.288Mhz, FSYNC input 384Khz; or BCLK input 1.536Mhz, FSYNC input 48Khz.

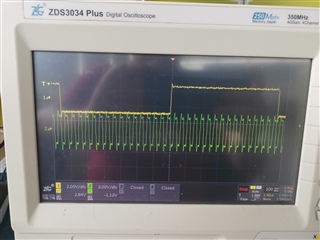

When I input 16Khz sine wave signal to IN1, the output signal after sampling is normal, as shown in the figure below:

Please provide me some advice.

Thanks for your help.