Other Parts Discussed in Thread: TLV320AIC1103

Hi,

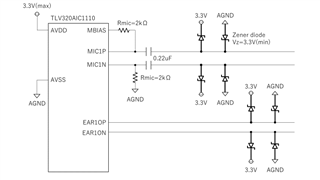

I have two questions about the power supply of the TLV320AIC1110.

Q1.

Is it OK as long as VDD adheres to the rated 2.7V~3.3V? In other words, does VDD need to be 3.0 V?

Q2

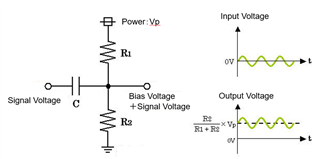

Is there any problem with the analogue power supply (AVDD, EARVDD) being separated from the digital power supply (DVDD, PLLVDD) by a coil and connected?

In slau090, p.22, it was connected to 3.3V_A via FB5 from DSP_3.3VDC, which is separate from 3.3V_D. Do 3.3V_D and 3.3V_A need to be completely separated?

Thanks,

Conor