Hi,

I'm trying to use the beep generartor on the TLV320AIC3100.

The chip output a square wave of 320Khz since I set register 71 D7 to 1. the signal is continous as the beep length register are not read.

I use a 12Mhz MCLk with the associate PLL as input clock.

I read back the register and all seem correct. I found out that "DAC PGA applied gain = programmed gain " in register 38 D4 and D1 stay at 0 indefinitly.

my configuration :

/*page 0*/

I2CSend(0,0);

I2CSend(1, 0x01);

usleep(1000);

/*page 3*/

I2CSend(0,3);

I2CSend(16,0x0C);//1MHz on internal RC

/*page 0*/

I2CSend(0,0);

I2CSend(4, 0x03);

I2CSend(5, 0x91);

I2CSend(6, 0x07);

I2CSend(7, 0x06);

I2CSend(8, 0x90);

I2CSend(11, 0x82);

I2CSend(12, 0x87);

I2CSend(13, 0x00);

I2CSend(14, 0x80);

I2CSend(18, 0x87);

I2CSend(19, 0x82);

I2CSend(20, 0x80);

I2CSend(25, 0x03);

I2CSend(27, 0x00);

I2CSend(60, 0x19);

I2CSend(63, 0xFC);

I2CSend(64, 0x00);

I2CSend(65, 0x30);

I2CSend(66, 0x30);

I2CSend(72, 0xC0);

I2CSend(73, 0x17);

I2CSend(74, 0x70);

I2CSend(75, 0x00);

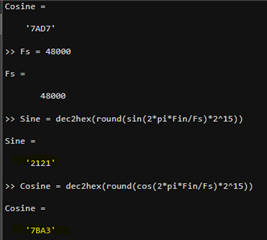

I2CSend(76, 0x21);

I2CSend(77, 0x21);

I2CSend(78, 0x7B);

I2CSend(79, 0xA3);

/*go to Page 1*/

I2CSend(0, 0x01);

/*Page 1*/

I2CSend(32, 0x86);

I2CSend(35, 0x40);

I2CSend(38, 0x80);

I2CSend(42, 0x1C);

/*Page 0*/

I2CSend(0, 0x00);

//I2CSend(71, 0x80);