Hi,

The TLV320AIC3104 datasheet's 8.5 Electrical Characteristics includes the following data.

Is this referring to the specifications of pins LEFT_LOP and LEFT_LOM?

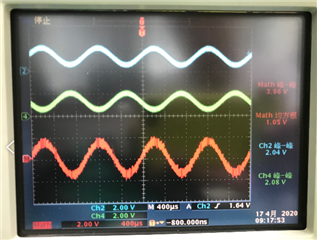

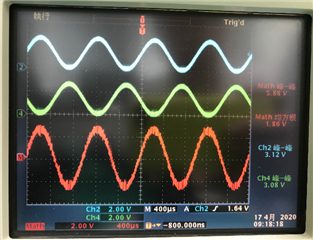

I have modified the register settings and measurements, resulting in LEFT_LOP and LEFT_LOM exceeding 4Vpp.

May I inquire about the maximum output Vpp of the pins LEFT_LOP and LEFT_LOM on the TLV320AIC3104IRHBR?

Thanks.

Kungyeh