Other Parts Discussed in Thread: PCM1680, PCM4104, PCM1690, PCM5121

Dear,

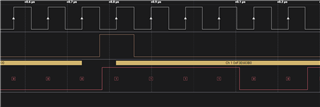

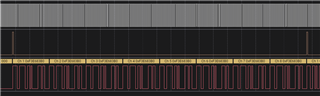

We using the PCM5122 4 times on a TDM bus of 48KHz 32bit audio samples.

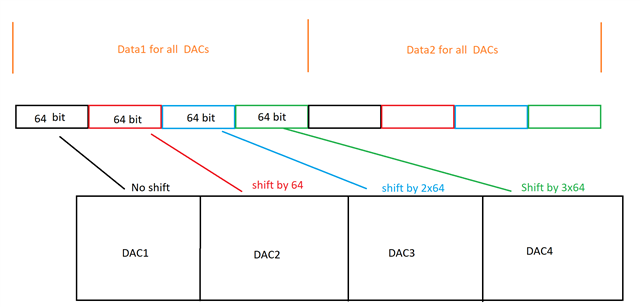

Each DAC has the same configuration, registers are identical except shift register 41.

The I2S Shift registers for DAC 1 = 0

The I2S Shift registers for DAC 2 = 64

The I2S Shift registers for DAC 3 = 128

The I2S Shift registers for DAC 4 = 192

On the TDM bus has each slot (8 in total) of each frame the same values.

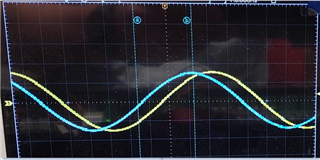

So each output must have the same signal.

For each DAC are the Left and right channels in phase

For DAC2, DAC3, DAC 4 are all the channels in phase.

But not for DAC1 and all the other DAC/channels.

It is only when we set in the phase register 41 the value 0 that the output signals are not more in sync.

The different is 1 LRCLK.

So we cannot understand that only our DAC1 isn't in phase with the other channels.

How we can resolve this issue?