Part Number: PCM1865

Hello, experts.

I was confused by the description on the datasheet(Rev.D 2018-Mar) regarding with the interrupt function.

I want to use the controlsense function in active mode, and interrupt function.

On page.57:

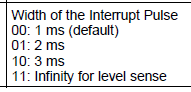

>The pulse width of the interrupt signal can be changed between 1ms, 2ms, 3ms and 4ms.

>The interrupt controlled cannot remain asserted, the status bits can be sticky, but the interrupt pin itself has no hold function.

On page.125:

>Bit1-0 WIDTH 1ms, 2ms, 3ms, Infinity for level sense

Q1:

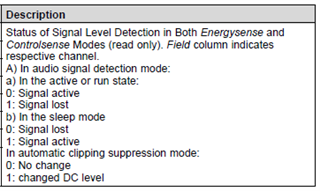

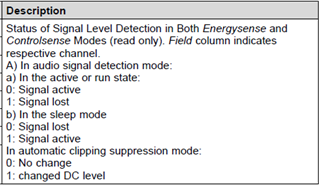

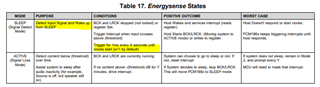

What is the target of "level sense"?

Energysense or Contolsense or Both?

Q2:

Intterupt events can be selected with Register #96.

- Clipping, DC Level Change(Controlsense), DIN, Energysense.

When ether or both events of "DC Level Change" and "Energysense" are triggered, can INT output pulse with infinite width?

Contrary, When "Clipping" or "DIN" events are tirggered, can the width of pulse be set to 1,2,3 or 4ms?

I'd appreciate it if you could give me advice.