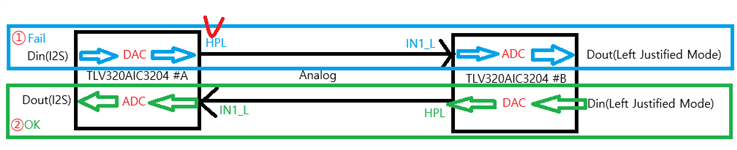

② #B to #A is normal.

① The voice received by Din(I2S 24bit) passes through the DAC and is not heard from the HPL. Is there anything I set wrong in the register below?

The register below is the register of #A.

The register of #B differs only by "0x1BC0".

(length of Audio Interface LJF - 16bit)

I couldn't hear the sound from HPL of #A, so I didn't check the ADC operation of #B.

u16 codec_initial_CH1_2[CODEC_SIZE] =

{

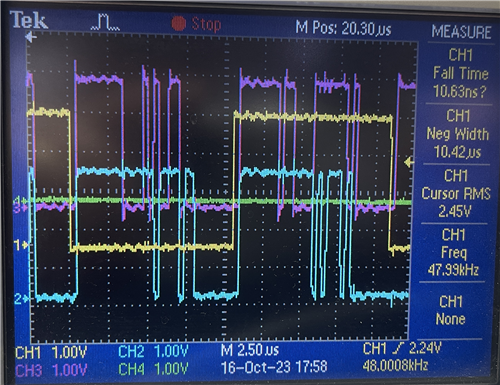

// MCLK = 11.2896Mhz(WCLK * 256) / BCLK = 2.8224Mhz(WCLK * 64) / WCLK = 44.1khz

// MCLK = 12.288 Mhz(WCLK * 256)) / BCLK = 3.072 Mhz(WCLK * 64) / WCLK = 48khz

// MCLK = 12.288 Mhz(WCLK * 128) / BCLK = 6.144 Mhz(WCLK * 64) / WCLK = 96khz

// PCM 24 Fix

////////////////Page 0////////////////// Example Page 87

0x0000, // Page 0

// 0x0101, // Reset

// 0x02~0x03, 0x06~0x08 PLL 설정.

0x0400, // MCLK pin is CODEC_CLKIN

///////////////DAC Set////////////////////

0x0B81, // NDAC = 1

0x0C82, // MDAC = 2

0x0D00, // OSR of DAC - 1

0x0E80, // OSR of DAC - 2 OSR = 128

0x1B20, // length of Audio Interface I2S - 24bit

0x3C01, // DAC - PRB_P1

///////////////ADC Set////////////////////

0x1281, // NADC // NDAC 값 사용.

0x1382, // MADC // MDAC 값 사용.

0x1480, // OSR of ADC - AOSR = 128 (Use with PRB_R1 to PRB_R6, ADC Filter Type A)

0x3D01, // ADC - PRB_R1

// 0x1900, // 사용 X

// 0x1A00, // 사용 X

// 0x1C00, // Data offset setting

// 0x1D00, // Loopback

// 0x2000, // Audio Interface 5 이해가 안되는 reg

// 0x2100, // Audio Interface 6 이해가 안되는 reg

// 0x24 ~ 0x2F // Read 전용

////////////////Page 1//////////////////

0x0001, // Page 1

0x0108, // Avdd On

0x0200, // Analog Blocks Enabled

///////////////DAC Set////////////////////

0x0300, // HPL uses Class-AB driver / PTM_P3

0x0400, // HPR uses Class-AB driver / PTM_P3

0x0930, // HPL, HPR Power On / LOL, LOR Off

0x0C08, // HPL - DAC Left routed

0x0D08, // HPR - DAC Right routed

0x1000, // HPL - Gain 0dB ★ Analog Gain // Mute - 0x1040

0x1100, // HPR - Gain 0dB ★ Analog Gain // Mute - 0x1140

0x1425, // Headphone Driver Startup 잘 모르겠음..예제따라함.

0x1675, // IN1L to HPL Volume Control -Mute

0x1775, // IN1R to HPR Volume Control -Mute

0x1828, // Mixer Amplifier Left Volume - Mute

0x1928, // Mixer Amplifier Right Volume - Mute

///////////////ADC Set////////////////////

0x0A00, // Full Chip Common Mode is 0.9V

0x3D00, // PTM_R4

0x4732, // Analog inputs power up time is 3.1 ms

0x7B01, // Reference will power up in 40ms when analog blocks are powered up

0x34C0, // IN1L Left MICPGA - 40k resistance

0x36C0, // CM is routed to Left MICPGA via CM1L with 40k resistance

0x37C0, // IN1R Right MICPGA - 40k resistance

0x39C0, // CM is routed to Right MICPGA via CM1R with 40k resistance

0x3B80, // Left MICPGA ★ Analog Gain

0x3C80, // Right MICPGA ★ Analog Gain

// 0x3E ~ 0x46 // Read 전용

////////////////Page 0//////////////////

0x0000, // Page 0

0x3FD6, // Left, Right DAC Power On

0x4000, // Left, Right DAC Not Muted

0x4100, // DAC Left Digital Volume 0dB ★

0x4200, // DAC Right Digital Volume 0dB ★

0x51C0, // Left, Right ADC Power On

0x5200, // Left, Right ADC Not Muted

0x5300, // Left ADC Digital Channel Volume 0dB ★

0x5400, // Right ADC Digital Channel Volume 0dB ★

};