Hi expert,

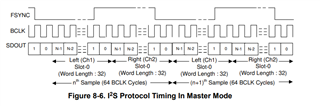

I didn't see clear detail about I2S format config in datasheet, only MD0 for master clock, does BCLK always 64 times the FSYNC frequency? Is 44.1kHz or 48kHz sample frequency realized by input MCLK(divide 256/512)?

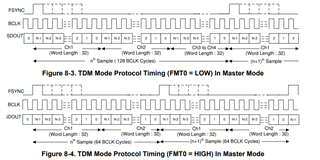

Does below picture mean TDM format can support 2-ch or 4-ch output, in different FMT0 config?