Dear teams,

There is an issue that our LSI cannot get ACK from the device when accessing registers via the I2C control port.

This phenomenon is occurring on our multiple test boards.

When accessing the I2C control port, we have confirmed that the startup sequence in the data sheet is met.

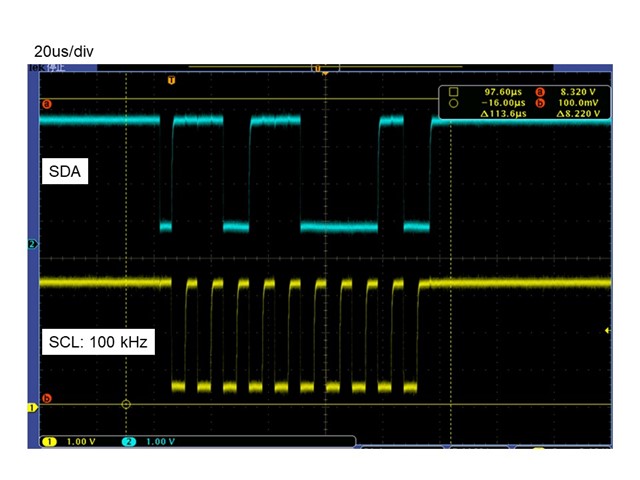

We have attached the waveforms we measured. Could you please take a look at it? The slave address is 0x6C, which is correct.

We have also confirmed that the AC characteristics of the I2C Control Port in the datasheet is met. Therefore, we don't think there is a problem with the waveforms.

Similarly, no ACK is returned for slave address 0x6D.

Have you reported any similar issue?

Could you please give me your advice regarding this problem?

Sincerely,

Takuma Ito