Other Parts Discussed in Thread: PCM1690,

Hello together,

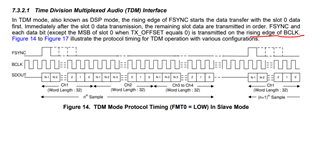

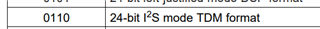

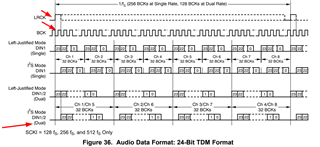

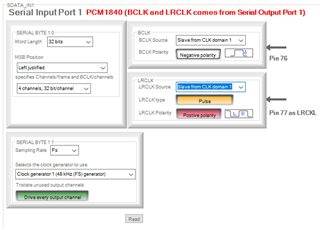

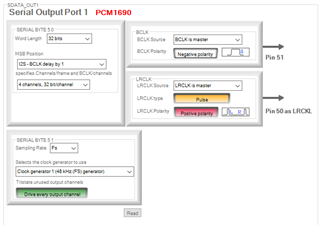

we use an PCM1840 as ADC while we are using the PCM1690 as DAC. For the PCM1840, we have configured it in Slave Mode (4-channel output with time division multiplexing (TDM) mode). For the PCM1690, we have configured it in Slave Mode 24-Bit I2S mode TDM format. Pictures below show our configuration.

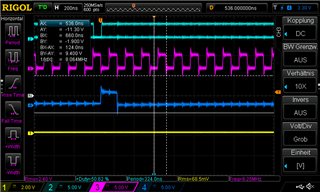

The clocks are shared between ADC and DAC and driven by a DSP which acts as clock master. We wonder a bit because it seems that the PCM1690 requires a positive BCLK while the PCM1840 seems to need a negative BCLK.

- Q1: Can you let us know at which clock transition the bits are sampled in the PCM1840 and PCM1690?

What we did to make it work is the following.

On the DSP data output we send the data in I2S mode with the clock set to negative polarity. Bits are sampled on the positive to negative transition. So this should perfectly fits the PCM1690 specifications, but those clocks are send to the PCM1840 as well, except for SDATA of course. On the DSP data input side, we sample left-justified. At the moment we sample here also on the positive to negative transition.

- Q2: Would it make here more sense to sample on the negative to positive transition (Thats why we would need to know the sample point of the PCM1840)?

- Q3:So far all of this seem to work, but we would want to know if you see any potential risks here as the clock requirements of both chips seem to differ?

PCM1840

PCM1690

DSP Settings:

Apart from this topic, we have sometimes a strange behaviour with the PCM1840.

When we boot up the system, it seems that it takes sometimes super long for the ADC to lock to the clocks. We rechecked the bootup behaviour and everything seems to be like specified, except for 2 points:

- Point 1 and Q4: Is that the BCLK has a negative polaritiy instead of a positive, as described above. Could this cause such a problem?

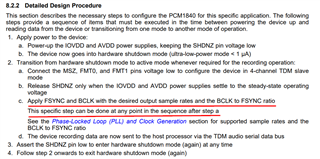

- Point 2 and Q5: The clocks are running before we release the ADC from Reset. In Page 28 of the datasheet it is mentioned that the clocks should be first active after step a. Is this really required? As this is not that easy when the ADC runs in slave mode.

Best regards,

Eric