Hi Team,

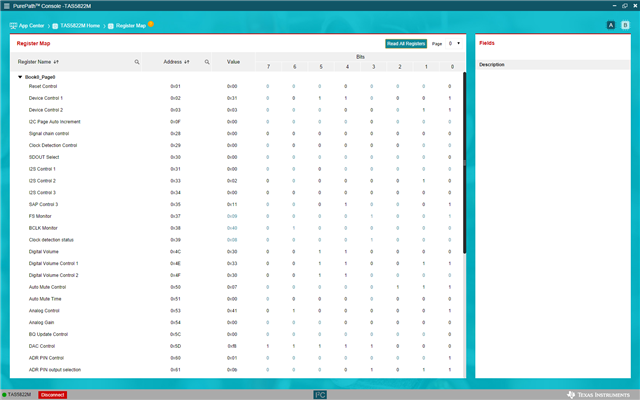

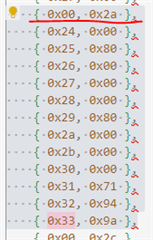

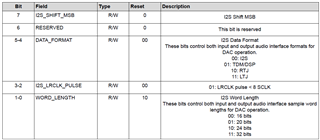

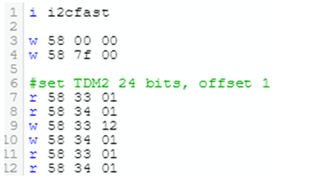

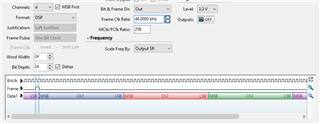

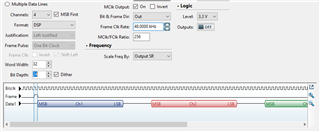

I have a customer who is looking at using TAS5822. They are currently facing issue with the exported register map value and the I2C read out( both read differently), even the initial start up before they do anything.

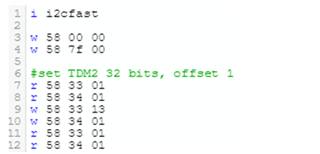

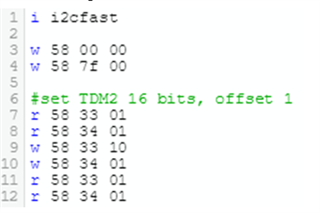

They tried to write some of the register thru the I2C, they can see the value are changed accordingly but when they try export the register map out and do a compare the value exported are different from what they have writen.

Could you please advise on this?

Thanks.