Hello,

Our customer plans to connect battery to TAS2781, Normal operation voltage is 9.0V and lowest is 4.0V, and there is another 3.3V fix power rail.

To take Y-bridge advantage, which Supply power mode is most suitable in this condition?

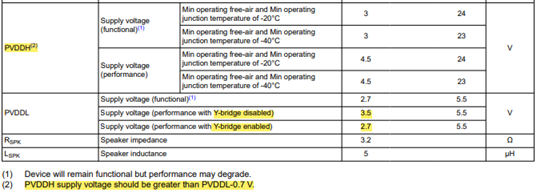

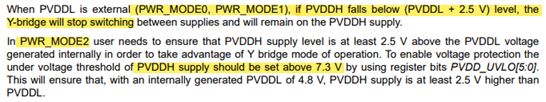

If we take MODE2, below 7.3V supply Y-bridge mode is stopped but the device still operate as simple H-bridge mode till 4.5V with performance guarantee and till 3.0V still D-amp can operate. In this mode external PVDDL supply is not required.

We think this will be the best choice, do you have another recommendation?

Here are related TAS2781 specification requirements and questions.

1. Audio performance is not guarantee if PVDDH below 4.5V, but D-amp functionality is guaranteed till 3.0V.

What is meaning of footnote (2)PVDDH should be greater than PVDDL-0.7V?

If PVDDL is 3.3V, then PVDDH should be greater than 3.3-0.7= 2.6V is it requirement?

2. PVDDL operation voltage requirement is changed between Y-bridge is engaged or not.

If it is related to PVDDH voltage is achieved 2.5V higher than PVDDL condition at Mode0 and Mode1, then below is correct expectation?

Y-bridge enable: PVDDL 2.7V(MIN)+2.5V = PVDDH 5.2V or Higher, performance guaranteed.

Y-bridge disable: PVDDL 3.5V(MIN)+2.5V = PVDDH 6.0 or Higher, performance guaranteed.

Why Y-bridge enable mode can accept lower, wider PVDDL voltage range? In disable mode PVDDL is not used for D-amp function..

Regards,

Mochizuki