Hello,

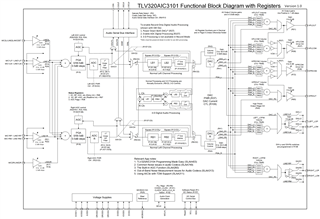

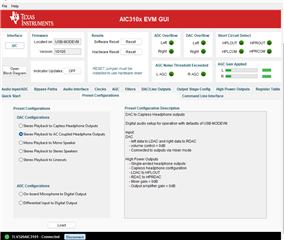

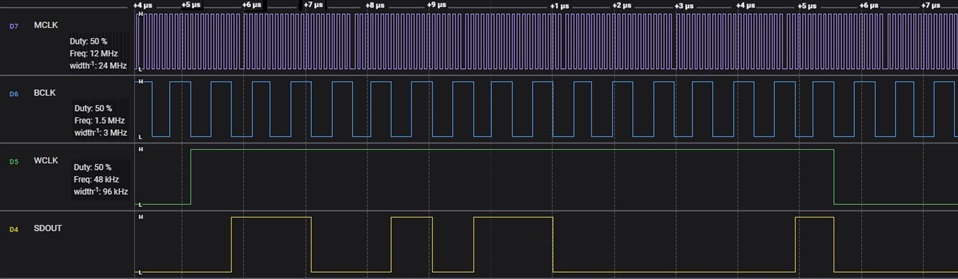

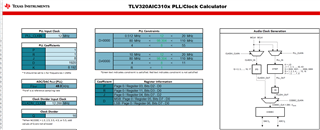

We are using TLV320AIC3101 chip that is connected to hub in our project. The hub is able to communicate with different audio codec chips via I2C and I2S interfaces. We have checked I2S signals with oscilloscope and they are fine. Initial sequence for codec configuration also looks fine but we are not sure about that because the TLV320AIC3101 does not generate valid audio output for headphones.

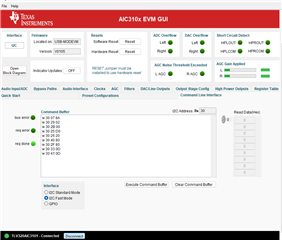

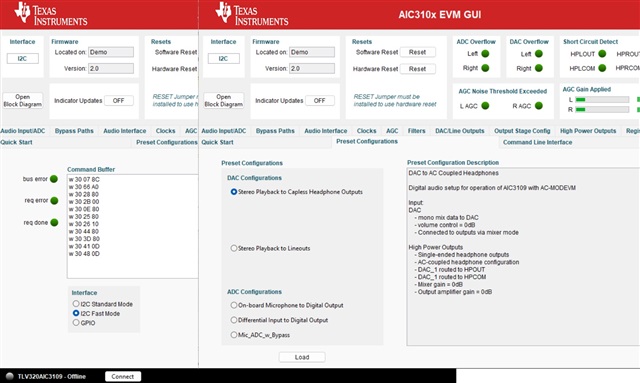

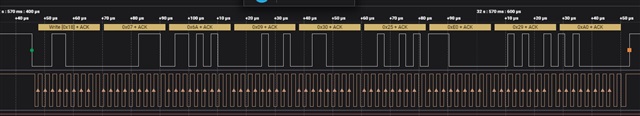

here is the I2C initial sequence caught with logic analyser:

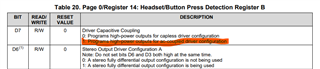

The codec responds with ACK bit for every message but is this right way of configuring it? The datasheet does not provide enough information about the initial sequence for codec configuration so we are not sure about the messages we need to generate. For now we are trying to modify registers 8, 9,14, 37, 41, 43, 44, but there is no output on audio side. Can you please check if there is something missing, or how should initial sequence for this codec look. Please keep in mind that we are using hub, not a controller so we are able only to put I2C commands in its registers, so it generate I2C initial sequence after the reset...

Thank you in advance!

Jovana Matkovic