Other Parts Discussed in Thread: OPA1679

Hi team,

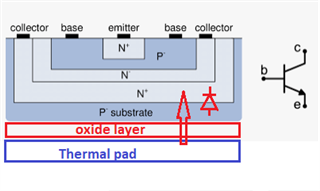

In OPA1679-Q1 datasheet, there are no specification for the thermal pad connection. So, my customer has connected the thermal pad to GND.

But in OPA1679 datasheet, it says that the thermal pad should be connected to V-. Also, it is explained in the related thread too.

Just too double check, the customer should not connect the thermal pad to GND, right? If so, could you update the datasheet for OPA1679-Q1 and write that the pad should be connected to V-?

Regards

Ohashi