Hello,Team,

I have questions about SRC4184IPAGT and CDCE913PW

・SRC4184IPAGT

Q1

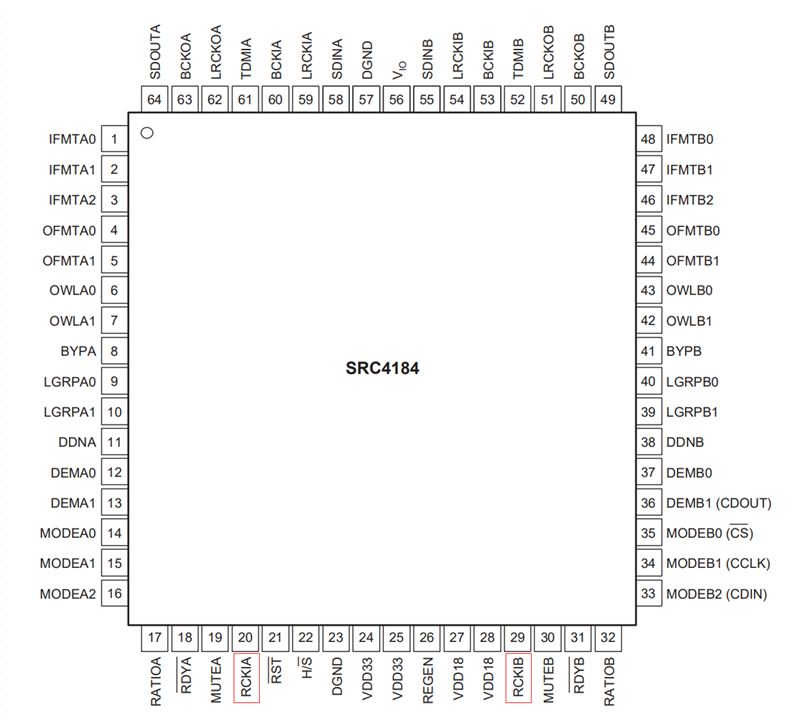

Are there any AC Operating Conditions which is related with RCKI,

for example, setup,hold and synchronization with BCKI/O,LRCKI/O,TDMIand so on.

Q2

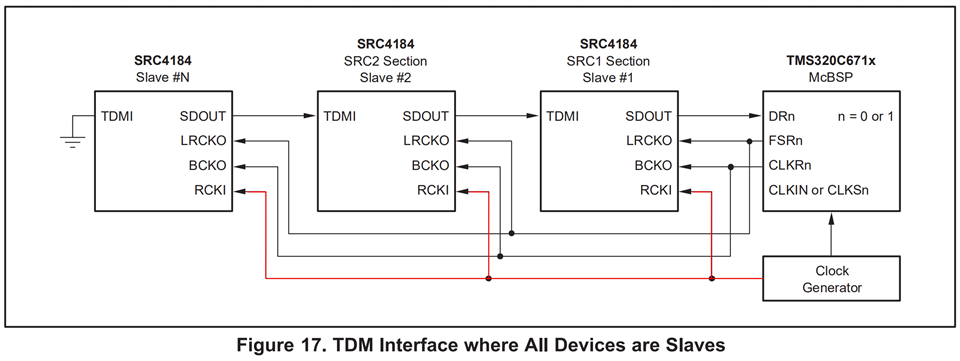

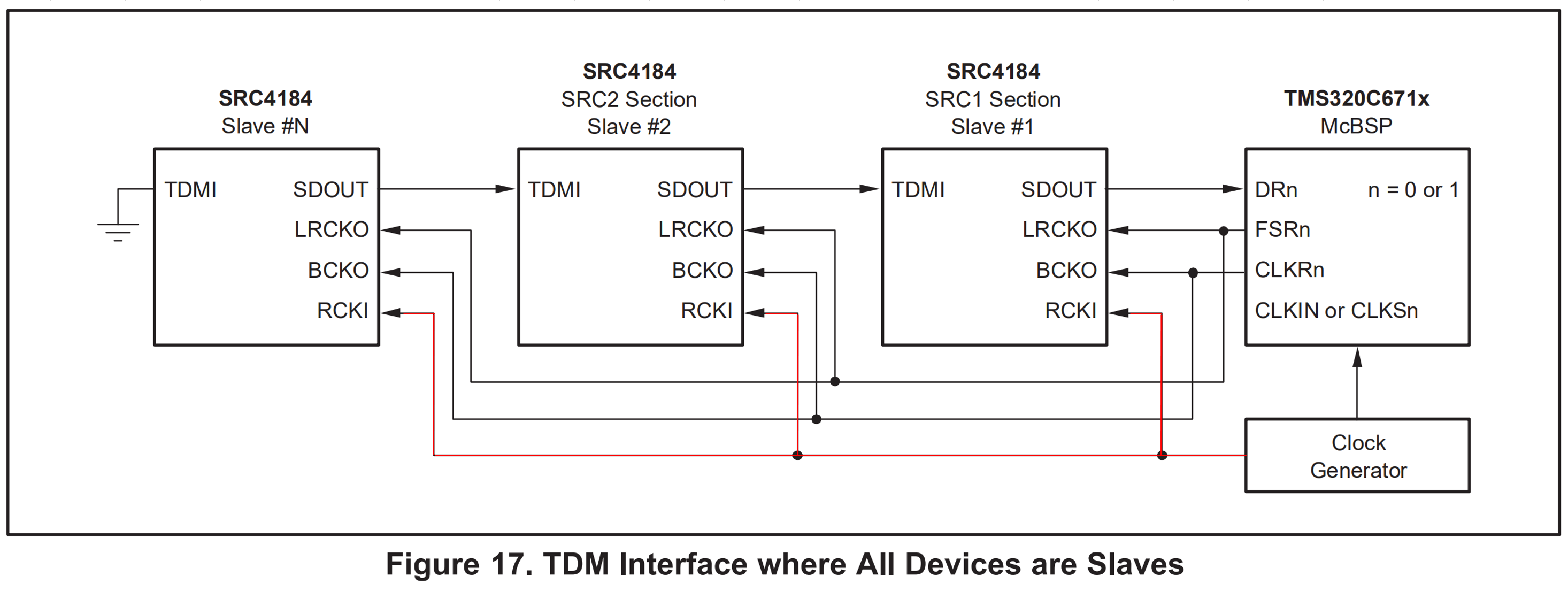

According to Figure17 in datasheet,i can see RCKI signal are inputed to each devices(SRC4184)which is controlled in slave mode from 1 clock generator which devide the line to 3 lines.

Should i devide clock signal from 1 clock generator? I mean, should i use RCKI to each devices in sysnc?

for example, in case using CDCE913PW for clock generator,CDCE913PW output CLK which is made from the same Pdiv1 and connect such as "Y1-SRC1/Y2-SRC2/Y3-SRC3",are there any problems?

・CDCE913PW

Q1

Is there any latency between Y1 to Y2/Y3, when this devide is set to use Y1,Y2,Y3 from Pdiv1?

Q2

Why is there difference about M,N,freq for PLL,in Clock Pro between when using only Y1 and when using Y1/Y2/Y3,in spite of using the same Inclock and the same out Freq setting.

I guess there is no change to set Y2/Y3 to use from Pdiv1 which is used for Y1 setting.

Anyway, in this case that this device to use Y1/Y2/Y3 the same freq and the same Pdiv,i can use reg setting refer to BitViewer in Clock Pro,is that OK?

Q3

In Clock Pro, why i cannot see reg15 nad 31 in BitViewer?

Q4

If i set reg"EEWRITE" to 1 for save the data to memory, is reg"EELOCK" set to 1 immediately without operating reg"EELOCK" setting?

Thank you for your support