Hello!

I am currently bringing up a prototype that has the TLV320ADC6140 for some line input audio and outputting on TDM.

The differential audio is AC coupled to the ADC and below are the I2C settings configured at startup:

// Wake from Sleep and use internal AREG

TLV320ADC_I2C_REG_SLEEP_CFG = 0b10000001;

// configure channel 1 as line input and enable DRE

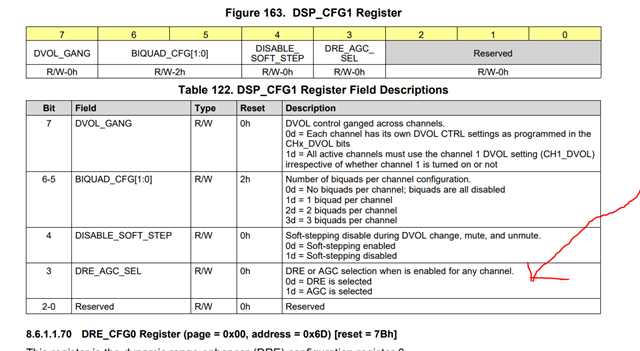

TLV320ADC_I2C_REG_CH1_CFG0 = 0b10000001;

// Enable Channel 1 Serial Output

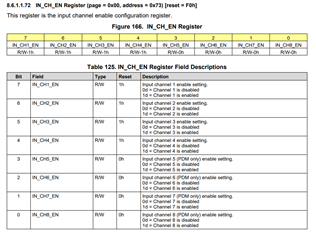

TLV320ADC_I2C_REG_ASI_OUT_CH_EN = 0b10000000;

// Power up ADC and PLL

TLV320ADC_I2C_REG_PWR_CFG = 0b11100000;

// Endless loop

while(TRUE){

pollStatusRegisters();

delay(LOOP_DELAY);

};

For testing, I have an Audio Precision APx555 being used as the input signal generator, and as the TDM Receiver. My device under test is acting as the TDM slave device, while the AP is set as Master.

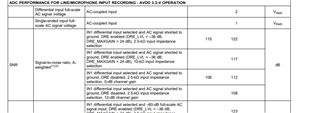

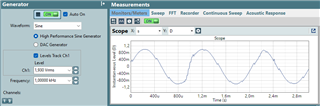

Generator is set to 1kHz Sine Wave adjusting level until hitting 0 dBFS (~1.93 VRMS)

Unfortunately, when enabling DRE with default settings, there is some distortion seen on the waveform.

Disabling DRE removes these distortions and THD+N is measured to be -92.18 dB

I've read through the DRE application note (SBAA400A – SEPTEMBER 2019 – REVISED DECEMBER 2023) and could not find anything to point towards what might be causing this issue.

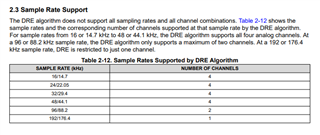

The sampling rate was set to 96kHz

Any ideas on what I might be doing wrong? Thanks in advance!